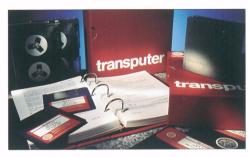

**DEVELOPING**

WITH THE

TRANSPUTER

INMOS is a member of the SGS-THOMSON Microelectronics Group

# **The Transputer Family**

- Powerful single chip processors

- Multiprocessing made simple

- Scalable performance

- Extensive software support

- Modular system design

- Reduced system cost

The transputer family is a range of 16 and 32-bit microprocessors supported by peripheral products and software and hardware development tools. The transputer is firmly established as the industry standard for parallel and multiprocessing, as well as being a powerful single chip processor. It is designed into a wide range of embedded systems and high performance computing applications.

This brochure describes the first generation transputer family, launched in 1985, and includes the IMS T225, IMS T400, IMS T425, IMS T426 and IMS T805 products. The second generation IMS T9000 family is described in detail in the IMS T9000 family brochure.

The transputer not only offers low system cost for single processor designs, but also offers a unique multiprocessing capability which allows the easy construction of modular systems with multiple transputers. This capability is derived from the transputer's fast on-chip serial communications links that overcome the bus bottleneck and shared memory constraints of other microprocessors. The performance of a transputer-based system is totally scalable because the processing bandwidth increases linearly as more transputers are added.

Software written in any of the standard languages such as C, C++, ADA or occam can be executed sequentially on a single transputer; the transputer's serial communications links and hardware scheduler allow the same program to be distributed as a series of processes over a network of transputers.

This gives designers the flexibility to build systems with unlimited performance and the ability to build a range of integrated products with processing power tailored to suit the cost/performance requirements of the end user.

The transputer family is supported by a complete range of software cross-development tools for Sun and PC hosts which enable customers to bring product to market ahead of the competition.

Compilers for ANSI C, C++ and occam are available, along with a wide range of standard software debug tools with special software support for message routing, profiling and performance optimisation.

For prototyping the target system, the modular *i***q** systems range of TRAMs (TRAnsputer Modules) has been developed to plug into motherboards for PC and VME based systems. Full details are given in the *i***q** systems Product Overview.

# **Transputer Architecture**

First generation transputers share a common architecture that gives software portability between any member of the family.

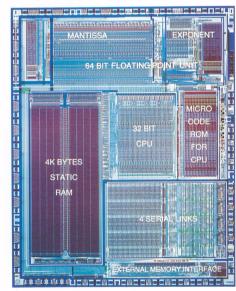

The microcoded CPU executes over 170 instructions, including single cycle instructions and application specific instructions e.g. 2D block move and CRC. It combines the advantages of RISC and CISC machines, giving peak performance of 30 MIPS. T8 series transputers also have an integral 64-bit IEEE 754 floating point unit, giving a peak 4.3 MFLOPS performance.

Instruction codes can vary in length and the CPU can fetch up to 4 single byte instructions simultaneously. The instruction queue is double buffered and can pipeline 4 instructions simultaneously, keeping the CPU fully

loaded and effectively decoupling the execution times from the memory speed.

16/32 bit System Processor Services Link Control **Timers** Link I/F On-chip Link I/F RAM Link I/F External Link I/F Memory Interface Event Generic block diagram of transputer

Floating Point Unit

2Kbytes or 4Kbytes of on-chip single cycle SRAM speeds up program execution and allows programs to run without external RAM.

The highly configurable external memory interface addresses 4Gbytes on the 32-bit processors and 64Kbytes on the 16-bit machines, and connects the transputer to external memory with minimal external support components.

Each transputer has 1µs and 64µs hardware timers.

The event logic provides an asynchronous handshake between an external event and an internal process and can be used as an interrupt. Context switching is fast - 630ns on a 30MHz transputer - because there are only a small number of registers needing to be saved. This is important for task switching and interrupt latency.

System services include an external 5MHz clock that drives an on-chip PLL for all clock speeds. Booting is from ROM or serial link. Reset/Analyse halts the transputer for debugging. Error indicates, for example, divide by zero, arithmetic overflow and so on.

IMS T805 die

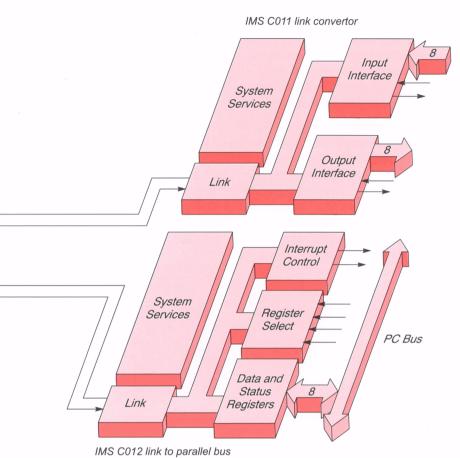

The links are bidirectional 2 wire serial links running at 5, 10 or 20 Mbits/s. They act as DMA channels for multiprocessor communications between transputers or with link adaptor chips to communicate with external peripheral components such as A/D convertors and graphics or SCSI controllers. Peripherals can also be mapped into the memory interface of the transputer.

The links are available as ASIC cells so that users can easily develop their own interfaces using semicustom technology.

| Family                          | Part      | Internal<br>memory<br>(Kbyte)      | Number of 20Mbit/s links | Speed<br>options<br>(MHz) | Package options               |

|---------------------------------|-----------|------------------------------------|--------------------------|---------------------------|-------------------------------|

| <b>T2</b> (16 bit)              | IMS T225  | 4                                  | 4                        | 20, 25, 30                | 68 PGA/PLCC, 100 QFP          |

|                                 | IMS T225M | 4                                  | 4                        | 20                        | 68 PGA, 100 CQFP, Mil Std 883 |

| <b>T4</b> (32 bit)              | IMS T400  | 2                                  | 2                        | 20                        | 84 PGA/PLCC, 100 PQFP         |

|                                 | IMS T425  | 4                                  | 4                        | 20, 25, 30                | 84 PGA/PLCC, 100 QFP          |

|                                 | IMS T426  | 4                                  | 4                        | 20, 25                    | 100 QFP. Parity on data bus.  |

| <b>T8</b> (32 bit + 64 bit FPU) | IMS T805  | 4                                  | 4                        | 20, 25, 30                | 84 PGA/PLCC, 100 QFP          |

|                                 | IMS T805M | 4                                  | 4                        | 20                        | 84 PGA, 100 CQFP, Mil Std 883 |

| <b>T9</b> (32 bit + 64 bit FPU) | IMS T9000 | 16                                 | 4x100Mbit/s              | 40, 50                    | 208 CLCC                      |

| Peripherals                     | IMS C011  | Link to I/O convertor/parallel bus |                          |                           | 28 DIL/SOJ                    |

|                                 | IMS C011M | Link to I/O convertor/parallel bus |                          |                           | 28 DIL/LCCC, Mil Std 883      |

|                                 | IMS C012  | Link to parallel bus               |                          |                           | 24 DIL                        |

|                                 | IMS C004  | 32 way crossbar                    |                          |                           | 84 PGA                        |

|                                 | IMS C004M | 32 way crossbar                    |                          |                           | 84 PGA Mil Std 883            |

|                                 | IMS C100  | Link convertor 20 to 100Mbit links |                          |                           | 100 QFP                       |

|                                 | IMS C104  | Router                             |                          |                           | 208 CLCC                      |

# Simple Single Processor Systems

The transputer has been specifically designed for low system cost. This is achieved by high on-chip integration, low pin count, low cost packages and reduced board area and cost because of the minimal external support requirements.

A single transputer can be used as an autonomous processor, since it has CPU, memory and communications links on-chip. In the majority of systems, program size dictates the use of external memory. The external memory interface is user programmable to DRAM, VRAM, SRAM, EPROM, EEPROM and flash ROM. A DRAM controller is included on the transputer. A single transputer system with 16 Mbytes of DRAM is the size of a standard credit card.

Transputers have low pin count - 68 to 100 pins - and need only four signal layer PCBs. The range of packaging includes low cost surface mount options. Power consumption is typically less than 1W; an IMS T400 has typical power consumption of 450mW.

A single 5MHz clock is all that is required to drive the transputer CPU and links, removing the need to route high speed clocks. Transputers can boot from ROM or serial link, eliminating the need for external ROM. The serial links offer reliable communications; only a 2 wire twisted pair is required for transmission up to 30cm with no external drivers. Links can be used for debugging the final system.

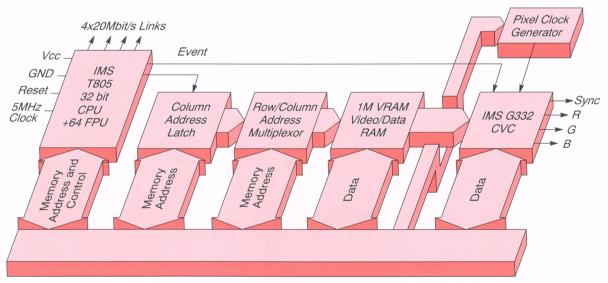

An example of a single processor system is the IMS B437 Compact Display TRAM which integrates an IMS T805 with 1 Mbyte of VRAM and an IMS G332 Color Video Controller. The transputer acts as a controller for the system and can run software such as CGI libraries supplied by INMOS. The IMS G332 CVC is programmable for displays up to 1024 x 1024 and up to 16 bits per pixel, supporting very high resolution images.

IMS B437 Compact Display TRAM

Graphics control system using IMS T805 processor and IMS G332 CVC

# Simple Multiprocessor Systems

The transputer's architecture has been designed for multiprocessing, with communication links and a hardware scheduler. The hardware scheduler allows the transputer to switch rapidly between software processes running on a single transputer.

Software programs can be written as a series of interacting processes that communicate via channels. On a single transputer these processes are timesliced and communicate through the memory of the transputer. On multiple transputers these processes can be allocated to separate transputers and run concurrently. Communication takes place via the serial links which are DMA channels memory mapped into the transputer. In ANSI C, a series of libraries support this programming activity and the occam language features parallelism and communications as highlevel language constructs.

Serial links are simple 2-wire connections requiring no glue logic, no snooping logic or bus arbitration. Standard bus architectures used for connecting conventional microprocessors limit realistic scalability to a small number of processors in a system. The upper limit for transputer scalability is rarely achieved, with current production systems using many thousands of transputers.

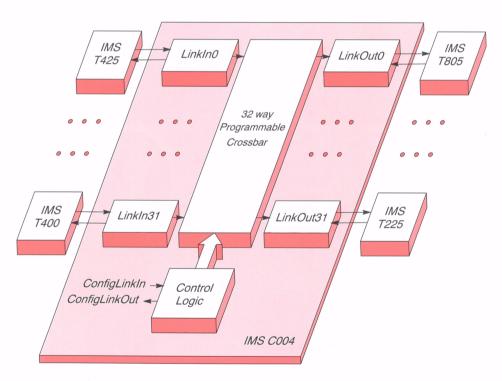

For building multiprocessor systems the IMS C004 32 way programmable crossbar switch provides full duplex communications between any member of the first generation transputer family. The IMS C004 is able to route from any of its 32 inputs to any of its 32 outputs. A control/configuration link is provided to allow an external processor to configure networks as required by the user.

Multiprocessor system using an IMS C004 crossbar switch

# Developing with the Transputer

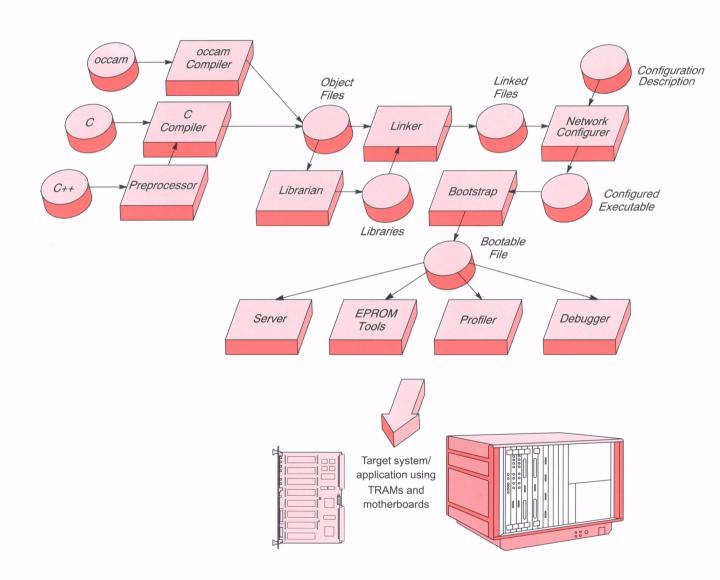

INMOS transputer development software has been designed around the concept of a set of compilers and tools known as a Toolset running on a host machine and targeting a development environment based on the *iq* systems range of TRAMS and motherboards.

There is also extensive 3rd party support, a list of which is available in the Transputer White Pages.

INMOS provides compilers for the most commonly used languages such as ANSI C, C++ and occam. These are available on industry standard hosts such as PC and Sun workstations. Full support tools and a comprehensive set of functions are supplied with the compilers giving I/O and a full ANSI C run time system.

INMOS has developed a server technology which interfaces between the transputer network and the host operating and file systems.

For debugging, interactive tools offer breakpointing, single stepping, and post mortem debugging. Toolset options include sophisticated profiling and performance analysis tools.

The target system can be a customer's own design or it can be prototyped using the range of  $i\mathbf{q}$  systems TRAMS and motherboards, allowing designers to demonstrate product concepts without investing in custom hardware up front. The Toolsets all support multiprocessing and multitasking.

# **Software Programming Model**

Programs written in ANSI C, C++ or occam are compiled to object files (TCOFF - Transputer Common Object File Format). Mixed language facilities are supplied with the Toolsets and assembly language inserts can be made for speed-critical sections. Library functions supplied by INMOS or the user can be linked into the program and the file configured to run on a single processor or network of processors. The program is automatically distributed over the transputer network.

Bootstrap code for booting from link or external ROM is supplied by INMOS and the bootable file run on the target hardware. This software can then be run with the debugger and profiler for testing and performance evaluation.

# **Software Development Products**

Software Toolsets contain the following tools and run on the host computer ( PC or Sun 4 compatible ):

- Compiler and libraries

- Linker and librarian tools

- Configuration for multiprocessor networks optimized message routing

- Bootstrap tools

- Basic interactive debugger for single/ multiprocessor programs (breakpointing and single stepping)

- ROM programming support tools

- Transputer memory interface design tool

- Mixed language programming support

- Server technology allowing transputer programs access to host operating system facilities

- Code/data placement control

- Program/hardware cross reference mapping

The INQUEST package contains a windowing debugger and performance optimisation tools. It is compatible with all the Toolsets described above and offers:

- Windowing operation (OSF/Motif and Microsoft Windows 3)

- Single stepping of transputer instructions and source statements (with threads)

- Conditional/Programmable breakpoints and watchpoints

- Source or assembly level views

- Programmable command language

- Program interrupt and restart facilities

- Percentage of time executing each procedure

- Percentage of time at high priority for transputer

- Idle time analysis for transputer

- Percentage of time in each process

- Utilisation of network over time displays an interactive chart.

- Remote download for booting over network

- Access to host O/S

- Integration of user supplied host services

- Distributed access to services

#### **ANSIC**

INMOS ANSI C Toolsets are validated using the Plum Hall C Validation Suite and certified by the British Standards Institute.

The following additional features are provided:

- Standalone and inline assembly language

- Inline functions for channel I/O and access to CRC, bit manipulation and memory block transfer instructions

- Source to bootstrap and startup code

- Libraries for transputer process creation and communications

Optimizations in the compiler include:

- Branch chaining, return chaining

- Peephole optimizations

- Workspace allocation, workspace colouring

- Common subexpression elimination

- Loop invariant code motion

- Dead code/redundant store elimination

Example C program

### C++ Preprocessor

The C++ Toolset, developed by Glockenspiel in conjunction with INMOS, implements C++ to the latest specification. The C++ Toolset works with the INMOS ANSI C Toolset.

#### occam 2

Established in 1982, occam 2 is a high level language being used for applications in real time control, imaging, communications and high performance computing. It is designed to express concurrent algorithms and how they are implemented on a single processor or a network of processors.

occam describes an application as a series of processes that communicate via channels. This makes a program simple to define, and allows a system with many separate functions to be built with a modular design. A set of interacting processes can be grouped as a single program for development purposes, allowing programmers to work on small manageable sections of the system.

occam can provide a degree of security not available to languages such as ANSI C. It is backed by formal methods and mathematical proof techniques. It supports structured concurrent programming and includes sophisticated error checking at compilation reducing, debug time and the risk of time dependent errors in the system. It makes an ideal language for system specification and behavioural description and, since it is easily mapped to hardware, it may also be used for hardware specification.

Since the development of occam and the transputer are closely related, they provide an efficient combination which can also be mixed with other languages such as C and assembler.

```

TIMER clock:

INT hours, minutes, seconds, date:

PROC update.time (INT now)

INT new.now, delta:

SEQ

clock ? new.now

delta := new.now MINUS now

now := new.now

... increment time/ date values

:

VAL one.hour IS ticks.per.second * 3600:

INT now:

BOOL running:

... Initialise

WHILE running

ALT

-- wait for a timeout

clock ? AFTER now PLUS one.hour

update.time (now)

ALT i=0 FOR users

request[i] ? command

SEQ

PAR

update.time (now)

response[i]! REQUEST.REGISTERED

CASE command

read.time

response[i]!hours, minutes,

seconds, date

... handle other requests

```

Example occam program

Compute TRAM

Application TRAM

**Development Hardware**

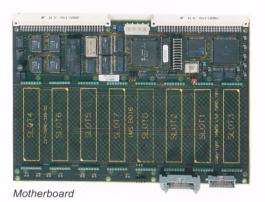

Transputer target systems can be constructed from hardware building blocks called TRAMs. TRAMs can be either compute TRAMs (combining a transputer and memory) or application specific TRAMs (interfacing a transputer to application hardware), e.g. graphics, image processing, Ethernet, or SCSI. Each TRAM is a self contained unit which uses the transputer serial links to interface to the outside world. This is an industry standard interface with many third party suppliers providing a wide range of additional functions to the INMOS products.

TRAM modules plug directly into TRAM motherboards such as PC/AT or VME bus format cards. TRAM motherboards provide a number of slots into which TRAMs can be fitted with the ability for the user to configure the network as required.

### **Prototyping and System Building**

TRAMs and motherboards offer a cost effective way of constructing prototype and production systems. These products are sold under the brand name *iq* systems, and allow demonstration of the feasibility of an application without building custom hardware.

iq systems products offer a modular upgrade path as new TRAMs become available. Products can be customised without complex hardware redesign.

### The IMS T9000 Family

The IMS T9000 will be available in TRAM module format for existing motherboards. In addition a new higher performance range of motherboards and modules will exploit the faster link and processing performance of the IMS T9000.

# Using iq systems to Construct a Target System

In order to develop any microprocessor based system it is necessary to build prototype systems for debugging and for demonstration to potential customers. This job is made simple by the modular architecture of  $i\mathbf{q}$  systems products.

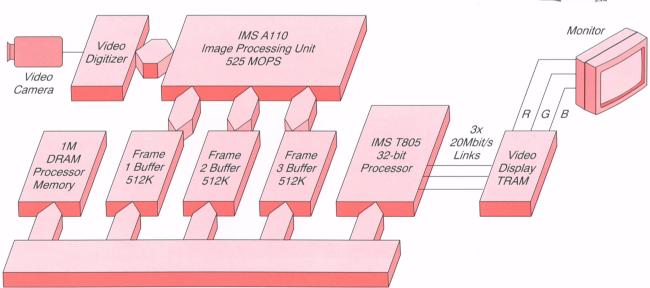

## **Image Processing and Display System**

A basic image processing system requires video capture, processing of the image or a region of interest and display of the processed image. This system could be assembled on a single 6U VME format card from off the shelf  $i\mathbf{q}$  systems components.

The IMS B429 Image Processing TRAM takes programmable resolution images in real time and perform 1 or 2D filtering using specialist IMS A110 image processing hardware. The TRAM can capture grey scale images at up to 20 frames/s and three frame buffers perform several filtering functions on the image prior to display.

The Image Processing TRAM is supplied with software libraries with common filtering functions such as image capture, display and convolution software.

Using 3 of the 4 transputer links the image can be transferred to the IMS B437 Graphics Display TRAM which will display the image on a VGA type display. Software support for the graphics TRAM includes CGI libraries.

Additional TRAMs could be added to the system such as an RS232 TRAM for mouse control and a Flash ROM TRAM for booting the system.

Image processing and display system

Toolset Software

PC Motherboard

2Mbyte TRAM

# **Building a PC Based Development System**

The benefits of the modular development system make it possible to customise the development environment. Below is an example of a basic single processor development system based around a PC.

### Software

Choice of ANSI C, C++ or occam 2 Toolsets

Software programs are compiled on the host PC and then downloaded to the target hardware for debugging. The server allows the user to make use of host facilities such as PC filing, screen, keyboard and DOS system functions.

#### **Hardware**

The target hardware can be installed inside the PC using the IMS B008 PC motherboard.

Alternatively the motherboard can be used as a gateway to an external system using a 20MBit/s transputer link for communication.

Transputers can be booted via the serial link, eliminating the need to program an EPROM for the target system.

A range of compute TRAMs are available with different speeds and sizes of memory. A 2Mbyte DRAM TRAM is recommended to start development. Further TRAMs can be added later as required.

### **PC Motherboard**

- 10 slots

- 200Kbyte/s interface to host

- Software / hardware configurable

- External link interface for chaining additional motherboards or connection to customer's own hardware.

## **Compute TRAM**

- Choice of transputer e.g. IMS T425 or IMS T805

- 2 Mbytes 4 cycle DRAM

- Size 2 module

- Subsystem port for local control of transputer network

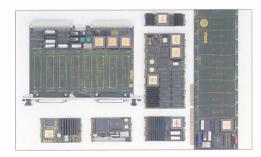

# Building an Ethernet Based Development System

For groups of programmers working on a project INMOS recommends the use of networked development systems. Using an ethernet network, developers can share a transputer target system.

The key to this environment is the IMS B300 Ethernet to Transputer Gateway which uses a standard TCP/IP protocol connection to provide access for up to four separately controlled and bootable networks of transputers. Data transfer is transparent to the user, and socket libraries interface programs over the TCP/IP Ethernet.

Software running on the IMS B300 and host manages the control and allocation of the central transputer resource amongst the users.

#### **Software**

- Choice of C, C++, and occam 2.

- Software is compiled on the host and downloaded to the target via the Ethernet connection. Hosts can be PC or Sun compatible systems.

- Connection manager software allocates the requested target hardware configuration, automatically searching for available transputers.

## Hardware

- IMS B300 Ethernet to Transputer Gateway

- Standard IEE802.3 Ethernet interface to transputer links.

- IMS B250 VME Rack

- Provides 12 slots for 6U VME boards such as IMS B014, IMS B016 VME master/slave board or other industry standard board.

- IMS B019 Differential System Port Board

- Buffers 4 transputer links via RS422 compatible drivers connecting the IMS B250 and the IMS B300.

- IMS B014 VME Motherboard

- 6U size board, takes up to 8 size 1 TRAMs.

- Compute TRAMs

- Choice of transputer and memory sizes.

Typical starter system may include four 8Mbyte

DRAM modules with IMS T805 transputers.

- Cables

- INMOS supplies a range of cables.

Software

Ethernet to Transputer Gateway

VME Rack

Range of TRAMs

Further product details are available in the Transputer Databook, *iq* systems Product Overview and the *iq* systems and Transputer Development Systems Databook. Contact your local sales office or distributor for further information.

## Sales Offices

#### **EUROPE**

#### DENMARK

**2730 HERLEV** Herlev Torv, 4 Tel. (45–42) 94.85.33 Telex:35411

Telefax: (45-42) 948694

## FINI AND

LOHJA SF-08150 Karjalankatu, 2 Tel. 12.155.11 Telefax: 12.155.66

94253 GENTILLY Cedex 7, Avenue Gallieni – BP 93 Tel. (33–1) 47.40.75.75 Telex: 632570 STMHQ Telefax: (33–1) 47.40.79.10

#### 67000 STRASBOURG

20, Place des Halles Tel. (33) 88.75.50.66 Telex: 870001F Telefax: (33) 88.22.29.32

### 6000 FRANKFURT

Gutleutstrasse, 322 Tel. (49-69) 237492 Telex: 176997 689 Telefax: (49-69) 231957 Teletex: 6997689=STVBP

### 8011 GRASBRUNN

Bretonischer Ring, 4 Neukerloh Technopark Tel. (49–89) 46006–0 Telex: 528211 Telefax: (49-89) 4605454 Teletex: 897107=STDISTR

## 5000 HANNOVER 51

Rotenburgerstrasse, 28A Tel. (49–511) 615960 Telex: 175118418 Telefax: (49–511) 6151243

#### 8500 NÜRNBERG 20

Erlenstegenstrasse, 72 Tel. (49–911) 59893–0 Telex: 626243 Telefax: (49-911) 5980701

## 7000 STUTTGART

Oberer Kirchhaldenweg, 135 Tel. (49–711) 692041 Telefax: (49-711) 691408

# 20090 ASSAGO (MI) V.le Milanofiori – Strada 4

Palazzo A/4/A Tel. (39–2) 89213.1 (10 lines) Telex: 330131, 330141 SGSAGR Telefax: (39–2) 8250449

#### 40033 CASALECCHIO DI RENO (BO)

Via R. Fucini, 12 Tel. (39–51) 591914 Telex: 512442 Telefax: (39-51) 591305

00161 ROMA Via A. Torlonia, 15 Tel. (39–6) 8443341 Telex: 620653 SGSATE I Telefax: (39-6) 8444474

#### **NETHERLANDS**

5652 AM EINDHOVEN Meerenakkerweg, 1 Tel. (31–40) 550015 Telex: 51186

Telefax: (31-40) 528835

#### 08021 BARCELONA

Calle Platon, 6, 4<sup>th</sup> Floor, 5<sup>th</sup> Door Tel. (34–3) 4143300 – 4143361 Telefax: (34–3) 2021461

#### 28027 MADRID

Calle Albacete, 5

Tel. (34–1) 4051615

Telex: 27060 TCCEE Telefax: (34-1) 4031134

#### S-16421 KISTA

Borgarfjordsgatan, 13 Box 1094 Tel. (46–8) 7939220 Telex: 12078 THSWS Telefax: (46-8) 7504950

### SWITZERLAND

#### 1218 GRAND-SACONNEX (GENEVA)

Chemin François-Lehmann 18/A Tel. (41–22) 7986462 Telex: 415493 STM CH Telefax: (41-22) 7984869

#### UNITED KINGDOM AND EIRE

### MARLOW, BUCKS SL7 1YL

Planar House, Parkway Globe Park Tel. (44–628) 890800 Telex: 847458 Telefax: (44-628) 890391

### **AMERICAS**

#### 05413 SÃO PAULO

Telex: (391)11–37988(UMBR BR)

Telefax: 11–551–128–22367

#### USA

NORTH & SOUTH AMERICAN MARKETING HEADQUARTERS 1000, East Bell Road Phoenix AZ 85022 (1)-(602) 867-6100

### SALES COVERAGE BY STATE

### ALABAMA

303, Williams Avenue, Suite 1031, Huntsville, AL 35801–5104 Tel.(205) 533–5995

#### ARIZONA

1000 Fast Bell Road Tel. (602) 867-6217

#### **CALIFORNIA**

200 East Sandpointe, Suite 120, Santa Ana. CA 92707 Tel. (714) 957–6018

2055, Gateway Place, Suite 300 San José, CA 95110 Tel. (408) 452-8585

#### COLORADO

1898, S. Flatiron Ct Boulder, CO 80301 Tel.(303) 449–9000

#### FLORIDA

902 Clint Moore Road Congress Corporate Plaza II Bldg. 3 – Suite 220 Boca Raton, FL 33487 Tel.(407) 997–7233

#### GEORGIA

6025, G.Atlantic Blvd Norcross, GA 30071 Tel. (404) 242 –7444

1300 E Woodfield Road Schaumburg, ILL 60173–5444 Tel. (708) 517–1890 Telefax: (708) 517-1899

1716, South Plate St. Kokomo, IN 46902 Tel. (317) 455–3500

### MASSACHUSETTS

55. Old Bedford Road Lincoln North Lincoln, MA 01773 Tel. (617) 259-0300

#### **MICHIGAN**

17197, N. Laurel Park Drive Suite 253, Livonia, MI 48152 Tel. (313) 462-4030

Staffordshire Professional Ctr. 1307, White Horse Road Bldg. F. Voorhees, NJ 08043 Tel. (609) 772–6222

### **NEW YORK**

2–4, Austin Court Poughkeepsie, NY 12603–3633 Tel. (914) 454–8813

## NORTH CAROLINA

4505, Fair Meadow Lane Suite 220 Raleigh, NC 27607 Tel. (919) 787–6555

1310, Electronics Drive Tel. (214) 466-8844

#### ASIA/PACIFIC

#### **AUSTRALIA**

**NSW 2027 EDGECLIFF** Suite 211, Edgecliff Centre 203–233, New South Head Road Tel. (61–2) 327.39.22 Telex: 071 126911 TCAUS Telefax: (61–2) 327.61.76

#### WANCHAI

22nd Floor - Hopewell Centre 183, Queen's Road East Tel. (852) 8615788 Telex: 60955 ESGIES HX Telefax: (852) 8656589

### **NEW DELHI 110001**

Liaison Office 62, Upper Ground Floor World Trade Centre Barakhamba Lane Tel. 3715191 Telex: 031–66816 STMI IN Telefax: 3715192

#### KOREA

# SEOUL 121 8th Floor Shinwon Building 823–14, Yuksam-Dong Kang-Nam-Gu Tel. (82–2) 553–0399 Telex: SGSKOR K29998 Telefax: (82-2) 552-1051

#### MALAYSIA

# **PULAU PINANG 10400**

4th Floor, Suite 4–03 Bangunan FOP, 123D Jalan Anson Tel. (04) 379735 Telefax: (04) 379816

## SINGAPORE

# SINGAPORE 2056

28 Ang Mo Kio Industrial Park, 2 Tel. (65) 48214 11 Telex: RS 55201 ESGIES Telefax: (65) 4820240

### TAIWAN TAIPEI

12th Floor 325, Section 1, Tun Hua South Road Tel. (886–2) 755–4111 Telex:10310 ESGIE TW Telefax: (886-2) 755-4008)

## **TOKYO 108**

Nisseki Takanawa Bld. 4F 2-18-10 Takanawa Minato-ku Tel. (81–3) 3280–4125 Telefax: (81–3) 3280–4131

Copyright © INMOS Limited 1992

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under patents, trademarks or other rights

. IMS and occam are trademarks of INMOS Limited