## Inside the Transputer

#### DAVID A. P. MITCHELL

BSc Researcher, Department of Computer Science Sheffield University

#### JONATHAN A. THOMPSON

BSc, MPhil Senior Experimental Officer, Department of Computer Science Sheffield University

#### GORDON A. MANSON

BSc, PhD, MSc Lecturer, Department of Computer Science Sheffield University

#### **GRAHAM R. BROOKES**

MA, PhD, MSc Professor of Computer Science, Department of Computer Science Hull University

#### **BLACKWELL SCIENTIFIC PUBLICATIONS**

OXFORD LONDON EDINBURGH BOSTON MELBOURNE © D. A. Mitchell, J. A. Thompson, G. A. Manson, G. R. Brookes, 1990

Blackwell Scientific Publications Editorial offices: Osney Mead, Oxford OX2 0EL 25 John Street, London WC1N 2EU 23 Ainslie Place, Edinburgh EH3 6AJ 3 Cambridge Center, Suite 208 Cambridge, Massachusetts 02142, USA 107 Barry Street, Carlton Victoria 3053, Australia

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without the prior permission of the copyright owner.

First published 1990

Printed and bound in Great Britain by Mackays of Chatham PLC, Chatham, Kent

#### DISTRIBUTORS

Marston Book Services Ltd PO Box 87 Oxford OX2 0DT (Orders: Tel: 0865 791155 Fax: 0865 791927 Telex: 837515

#### USA

Publishers' Business Services PO Box 447 Brookline Village Massachusetts 02147 (Orders: Tel (617) 524–7678)

Canada

Oxford University Press 70 Wynford Drive Don Mills Ontario M3C 1J9 (Orders: Tel (416) 441–2941)

Australia

Blackwell Scientific Publications (Australia) Pty Ltd 107 Barry Street Carlton, Victoria 3053 (Orders: Tel: (03) 347–0300)

British Library

Cataloguing in Publication Data

Inside the transputer. — (Computer science texts).

1. Multiprogramming microprocessor systems

I. Mitchell, David A. P. II. Series 004'.32

ISBN 0-632-01689-2

Library of Congress Cataloging in Publication Data Inside the transputer/David A. P. Mitchell . . . [et al.]. p. cm. –(Computer science texts) Includes bibliographical references. ISBN 0-632-01689-2 1. Transputers. I. Mitchell, David A. P. II. Series. TK7895.T73155 1990 621.39'16—dc20

## Contents

#### Preface, vii

#### 1 The Transputer, 1

- 1.1 Background, 1

- 1.2 The occam Language, 2

- 1.3 Processes and Concurrency, 3

- 1.4 occam Instructions, 4

#### 2 Transputer Hardware Description, 12

- 2.1 Introduction, 12

- 2.2 Registers, 14

- 2.3 The Workspace Pointer, 15

- 2.4 The Instruction Pointer, 16

- 2.5 The Operand Register, 17

- 2.6 Communications Links, 18

- 2.7 Communication Protocol, 20

- 2.8 Errors, 21

- 2.9 Time, 22

- 2.10 Reset, Analyse and Booting, 23

- 3 Instruction Set Overview, 26

- 3.1 Addressing and Memory Access, 26

- 3.2 Arithmetic and Logical, 29

- 3.3 Branching and Program Control, 33

- 3.4 Process Scheduling and Control, 35

- 3.5 Inter-process Communication, 41

- 3.6 Miscellaneous, 48

- 4 Example Programs, 51

- 4.1 Introduction, 51

- 4.2 Introductory Examples, 52

- 4.3 Communication Examples, 58

- 4.4 Description and Examples Using the ALT Instructions, 67

- 4.5 An Example of Recursion Within a GUY Construct, 75

- 4.6 Idle Time Example, 76

- 4.7 Simple Loader, 80

- 4.8 Conclusions, 85

- 5 Reference Section, 87

#### Appendices

- A Transputer Opcodes, 224

- B Symbols, 225

- C Workspace Usage, 226

- D Instruction Cross-references, 227

Bibliography, 229

Index, 230

# Preface

The transputer is a family of high performance microprocessors produced by INMOS Limited. One of its most significant features is the ability to perform multi-tasking in hardware, with sub-microsecond context switching. Communication between processes is also provided by hardware, both for internal data transfers, and transfers between different processors.

Unfortunately, there is a dearth of information regarding low-level aspects of the transputer. For a long time, INMOS claimed that since the transputer was specifically designed to efficiently execute the high-level language occam, it was not necessary for programmers to be aware of the machine-code instruction set. They have since had a change of heart, and have released *The Compiler Writer's Guide* [4], which describes the instruction set from the point of view of someone wishing to produce a compiler, as well as giving a brief formal definition of each instruction.

While The Compiler Writer's Guide is very good in what it sets out to achieve, it fails to show how the transputer works. For example, it is possible, using a short sequence of instructions, to make a process running on a transputer sleep while waiting for one of several events, such as input from a channel, or a particular time to come to pass. The Compiler Writer's Guide explains how to code such an instruction sequence; what it does not tell you is how this particular instruction sequence actually works. In this book, we have set out to fill this gap.

Chapter 1 gives an introduction to the transputer and occam, while chapter 2 describes the transputer's architecture.

Chapter 3 gives an overview of the instruction set. We have arranged this chapter from the point of view of a machine-code programmer, rather than a compiler writer. For example, all instructions that cause a branch or change in execution address are dealt with together, whereas in *The Compiler Writer's Guide* they would be dealt with under different categories, such as loops and procedure calls.

Chapter 4 contains many examples of programs written in machinecode, both to give a feel for assembly language programming, and to show some of the things that are impossible to do from occam.

Chapter 5 forms a reference section. Here, each transputer instruction is defined, one per page. We have included a formal definition for each instruction, which we have tried to make as readable as possible, whilst maintaining preciseness. There then follows an informal description of each instruction and finally, in most cases, a short example showing a typical use for that instruction.

Overall, we see this book as being complementary to, rather than in competition with, *The Compiler Writer's Guide*, and would recommend that the reader obtains a copy of that document too.

We have only included the 'core' transputer instructions in this book, that is to say, ones that are implemented on the T414. This has been done chiefly due to time and space considerations. Nevertheless, these instructions include amongst other things, all the process scheduling and communication instructions, which are the ones most in need of a detailed description.

The authors wish to acknowledge the assistance and encouragement of colleagues at both the Universities of Sheffield and Hull during the preparation of this book.

Finally, please note that INMOS and occam are trademarks of the INMOS group of companies.

## Chapter 1

## The Transputer

### 1.1 Background

In 1985 the transputer was first revealed to the world. At that time it was heralded as a revolution in computing. The first processor in the transputer series, the T414, boasted an unprecedented speed of 10 MIPS (millions of instructions per second), together with the ability to perform multitasking in hardware. Dedicated on-chip link controllers allowed for communications between processes running on different transputers, with minimal processor overhead. The T414 is a 32-bit processor with 2K of on-chip RAM and four interprocessor links, addressing up to 4Gbyte of external memory using multiplexed address and data lines.

Since then, various other members of the transputer family have been announced or released.

- The T212, a 16-bit version with 2K of onboard RAM and a 64K address range, using separate address and data buses.

- The M212, a T212 with two of the four links replaced by built-in disc controller circuitry.

- The T800, essentially a revamped T414 with a floating-point coprocessor integrated onto the chip, extra instructions, improved links and the onboard RAM doubled to 4K. This chip to a large extent has established the transputer's reputation, since it combines high performance floating-point processing (1.5 MFLOPs sustained) with the possibilities of parallel processing.

- The T222, a revamped T212 with 4K of onboard RAM.

- The T801, a T800 with separate address and data buses for faster memory accesses.

#### Chapter 1

• The T425 and T805, upgraded versions of the T414 and T800 with extra instructions added to facilitate single-stepping, and other such debugging aids.

When the T414 was first released, INMOS decided to match the idiosyncratic nature of their new baby by their approach to marketing. For example, while trying to emphasise the novel and revolutionary aspects of their new processor, they more or less forgot to tell the general public that the T414 was in fact actually a microprocessor. An unusual and iconoclastic microprocessor perhaps, but a microprocessor nevertheless. Part of the problem was INMOS's insistence that the programming language, occam, was the "assembly language for the transputer", and that the transputer should always be programmed in occam.

occam is a high level language with strong support for parallel processing, and the transputer and occam were jointly developed with each other in mind. Consequently, occam programs compile to very compact, very efficient object code when the target processor is a transputer. This is quite a bit different from saying that occam is an "assembly language". Also, since the transputer is designed to execute compiled occam efficiently, it follows that it should work reasonably well with other high level languages, since occam has the same sorts of features such as loops, procedure calls and the like.

The consequences of INMOS's early approach meant that engineers were unable to run their beloved FORTRAN programs, and people wishing to use the transputer at a low level were denied use of assembly language. This last point is significant, since there are some things which simply cannot be done from occam—such as an idle time counter. This led to various groups of people (the authors included), poking around in the innards of the transputer, trying to ascertain what the various transputer instructions were, and what opcodes were associated with them. This soon led to a state of potential anarchy, with people making up their own mnemonics for each instruction, and often confusing instructions for similar-appearing ones (such as addition and indexing). Finally, INMOS relented, resulting in the release of *The Compiler Writer's Guide*, as well as FORTRAN, Pascal and C compilers.

## 1.2 The occam Language

Since the occam programming language is closely related to the transputer, and since some transputer instructions exist specifically to implement certain occam constructs, it is necessary to have at least a basic knowledge of occam to get the most out of this book. The rest of this chapter introduces the main features of occam; for more detailed coverage, the reader is referred to other books on the subject [1,2].

#### **1.3 Processes and Concurrency**

The transputer architecture uses processes as the fundamental standard software building block, and it provides the direct implementation of a process in hardware. A process is an independent computation which is able to communicate with other processes which are being executed at the same time. The communication between processes running on transputers is achieved by explicitly defined channels. A process itself can consist of subprocesses by time-sharing.

The transputer provides a number of links which support point-topoint communications between transputers, thereby enabling processes to be distributed over a network of transputers. Hence it is possible to program systems containing multiple interconnected transputers in which each transputer implements a set of processes. However it needs to be noted that the transputer can only communicate directly with another one to which it is physically wired. It is the ability to specify a hardwired function as an occam process which provides the architectural framework for transputers with specialised functions such as graphics.

When a pair of processes communicate with each other, one of the processes outputs a message to the channel and the other inputs the message from the same channel. The important point is that with these channels the communications are synchronised and unbuffered. When a channel is used to connect two processes, then the communication can only take place when both the input and output processes are ready. Whichever process reaches its input or output statement first, must wait until the other process is ready. Once both processes are ready then the inputting and outputting can proceed. This form of communication is equivalent to handshaking in other hardware systems. It provides the necessary level of process synchronisation.

A process may be ready to communicate on any number of channels. Communication takes place when another process is ready to communicate on one of the channels. Since the process itself may have internal concurrency, it may have many input channels and output channels performing communications at the same time.

#### **1.4 occam Instructions**

In occam, programs are built up from processes. Each process may be regarded as a 'black box' with some particular internal state. The processes are finite, such that each process starts, performs a number of actions and then terminates. The simplest process is an action, and an action consists of an assignment, an input or an output. Processes may be combined together to form programs by way of process constructors. Since each process may itself consist of other processes, some of which may execute in parallel, the concept of processes as used in occam means that there is a large amount of internal concurrency in the language. The degree of concurrency that can actually be achieved at any given time will alter as processes start and terminate.

Ultimately all processes are constructed from five primitive processes, namely:

- (1) assignment,

- (2) input,

- (3) output,

- (4) SKIP,

- (5) STOP.

An assignment computes the value of an expression and sets a variable to this value. An assignment is indicated by the symbol :=. The example

b := e

sets the value of the variable b to the value of the expression e and then terminates. Thus,

y := 0

sets the value of y to zero.

Input is used for communicating between processes. Input is indicated by the symbol ?. In the example,

d ? y

a value from the channel d is input and assigned to the variable y and then the process terminates.

Like input, output is used for communicating between processes. Output is indicated by the symbol !. In the example, d ! e

the value of the expression e is output to the channel d and then the process terminates.

The SKIP process is a null process, that is, it simply terminates immediately without any further processing. On the other hand, the STOP process begins executing but never terminates.

A number of processes may be combined to form a construct. A construct is itself a process and so can be used to form part of a further construct. Each component process of a construct is written two spaces further from the left hand margin so as to indicate that it is part of the construct, and acts as a 'guard' for that particular construct. There are four main classes of construct:

| (1) | SEQ   | sequential  |

|-----|-------|-------------|

| (2) | PAR   | parallel    |

| (3) | IF    | conditional |

|     | WHILE | conditional |

| (4) | ALT   | alternative |

The SEQ constructor specifies that the processes which follow are to be performed in a sequential manner, so that for example,

> SEQ process1 process2

means that *process1* is executed first, followed on its completion by *process2*. The whole sequence terminates when the last process, in this case *process2*, has itself terminated. It is again emphasised that in occam the level of indentation following a given constructor is important, and consists of two spaces. This specifies the range of that constructor and acts as a guard for those processes.

In the example,

```

SEQ

c1 ? x

x := x + 1

c2 ! x

```

a value is input on channel c1 and assigned to the variable x. Then x is incremented by 1, and finally the result is output on channel c2.

To provide concurrency, the constructor PAR means that processes are executed in parallel. For example,

```

PAR

process1

process2

```

means that *process1* and *process2* execute in parallel with each other. The processes must be independent of each other, and the construct terminates only after all the component processes have terminated; but there is no fixed order in which the individual processes will terminate. For example,

```

PAR

c1 ? x

c2 ! y

```

allows the communication of input on channel c1 of the variable x, and output on the channel c2 of the variable y to take place together, i.e. concurrently. This parallelism is highly optimised so as to incur minimal process scheduling.

There also exists a conditional construct:

```

IF

condition1

process1

condition2

process2

```

where condition1 and condition2 represent conditions whose values may be either true or false. This construct is such that process1 will be executed if condition1 is true, otherwise process2 is executed if condition2 is true, and so on. Only one of the processes is executed, and then the construct terminates. For example,

```

IF

x = 0

y := y + 1

TRUE

SKIP

```

increments the value of the variable y only if x is zero. It is important in this construct that at least one of the conditions is *true*, or the construct will behave as a STOP and the process will halt. In the above example this criteria is provided by the use of the SKIP.

Another form of conditional construct is that of the WHILE construct. In this construct,

> WHILE condition process

the process is continuously executed until the value of the condition is false. For example,

WHILE x > 5 x := x - 5

leaves x with the value of (x remainder 5) if x is positive.

A further construct is the ALT, or alternative, which provides a selection between processes. The ALT construct takes the list of processes within its guard and performs the first process that it finds which satisfies its appropriate guard condition. For example,

```

ALT

guard1

process1

guard2

process2

guard3

process3

```

waits until one of the guard conditions guard1, guard2 or guard3 is ready. A guard condition consists of an event to wait for, such as channel input, plus an optional boolean value. (If this value is false, then the guard is ignored.) If guard1 is ready first then process1 proceeds, similarly if guard2 becomes ready first then process2 will be executed, and so on. Only one process will be executed, and then the ALT process terminates when the process which has been chosen itself terminates. Note that if all the guards have their optional boolean value set to false, then the ALT construct behaves as a STOP. An example ALT construct is,

```

ALT

(counter < max) & chan ? data

SEQ

sum:= sum + data

counter := counter + 1

total ? signal

```

```

SEQ

out ! sum/counter

counter := 0

sum := 0

TRUE & SKIP

SKIP

```

which undertakes one of the following:

- (1) when there is data on channel *chan* and the counter is less than some limit *max*, inputs *data*, adds it to *sum* and increments a count, *counter*, or

- (2) when there is a signal on the channel *total*, outputs on the channel *out* the average of the data read in, and resets the variables *counter* and *sum*, or

- (3) does nothing

In addition to the constructs which have been discussed so far, a replicator may be used with a constructor in order to repeat a process a number of times. For example,

```

SEQ i = 0 FOR n

process1

```

causes process1 to be repeated n times. Or, for a parallel construct,

```

PAR i = 0 FOR n

process(i)

```

constructs an array of n similar processes, process(0), process(1), ..., process(n-1).

A replicated ALT construct also exists which consists of a number of identically structured alternatives, each of which is triggered by input from a channel. For example, a multiplexer might be provided by,

```

[20] CHAN OF INT In:

CHAN OF INT Out:

PAR

... processes providing data on In channels

WHILE TRUE

INT y:

ALT i = 0 FOR 20

In[i] ? y

Out ! y

... processes taking data from out channel

```

This example monitors 20 input channels In, and when any one has any data, then the data from the appropriate In channel, is passed to the *Out* channel. Hence communication from the 20 In channels is merged into the *Out* channel.

In occam, every variable, expression and value has a type, which may be a primitive or an array type. The type defines the length and interpretations of the type. The following are the types which are present in all implementations of occam:

- CHAN Each communication channel provides one way communication between two concurrent processes TIMER Each timer provides a clock which can be used by

- any number of concurrent processes

- INT INT is a signed integer whose range is chosen by the compiler to be easily implementable on the target machine.

In addition, it is possible to specify explicit integer ranges:

> INT16 -32768...32767INT32 -2147483648...2147483647INT64  $-2^{63}...2^{63} - 1$

- REAL32 Floating point numbers using a sign bit, 8 bit exponent and 23 bit mantissa

- REAL64 Floating point numbers using a sign bit, 11 bit exponent and 52 bit mantissa.

A variable, expression or value may be declared to be one of the above types by use of a declaration of the form

Тх:

meaning that x has been declared to be of type T, where T may be a new channel, variable or timer. The declaration is terminated by the use of a colon. For example,

INT x : process1

declares x as an integer to be used in process1.

Array types are constructed from components. For example,

[n] T

is an array constructed from n components of type T. A component of an array may be selected by subscription, so that,

v[e]

selects the component e of array v. A set of components of an array may also be selected by subscription. For example,

[v FROM e FOR c]

selects the components v[e],  $v[e+1], \ldots, v[e+c-1]$ .

It is often useful to be able to refer to a process by name. This may be done using the definition PROC. For example,

```

PROC square (VAL INT n, INT sqr)

sqr := n * n

:

```

defines the name of the process square. This may be referred to elsewhere in the program. For example,

square (x,sqrx)

means

sqrx := x \* x

In the discussion so far, several operators have been assumed to exist, such as +, -, and \*. The operators which are available in occam are given below.

| Operator               | Operand type  | Description          |

|------------------------|---------------|----------------------|

| +,-,*,/                | integer, real | arithmetic operators |

| PLUS,MINUS,TIMES,AFTER | integer       | modulo arithmetic    |

| =,<>                   | any primitive | relational operators |

| >,<,>=,<=              | integer, real | relational operators |

| AND, OR, NOT           | boolean       | boolean operators    |

| BITAND,BITOR,><,BITNOT | integer       | bit operators        |

| <<,>>                  | integer       | shift operators      |

In the previous section, the provision of interprocess-communication through occam channels was discussed. These channels provide pointto-point communications which ensure that messages are both synchronised and unbuffered. By this means the requirement of process synchronisation is ensured within the language itself. We can illustrate

10

such synchronisation in the consideration of a simple queue. The program considers data as flowing down a pipeline represented as a series of slots, where the slots form an array of parallel processors which pass data between adjacent slots. A simple approach to this might be:

```

[20] CHAN OF INT slot:

PAR i := O FOR 19

WHILE TRUE

INT y:

SEQ

slot[i] ? y

slot[i+1] ! y

```

Here we define an array *slot* of 20 channels, and use a replicated PAR construct so that 19 parallel processes are set up which continually transfer data between adjacent slots in the queue. The synchronisation between successive slots is achieved by the SEQ construct. However it should be noted that this represents only a fragment of a program, and in particular it does not provide a mechanism for input into slot[0], or any effective output for data from slot[19].

## Chapter 2

# Transputer Hardware Description

## 2.1 Introduction

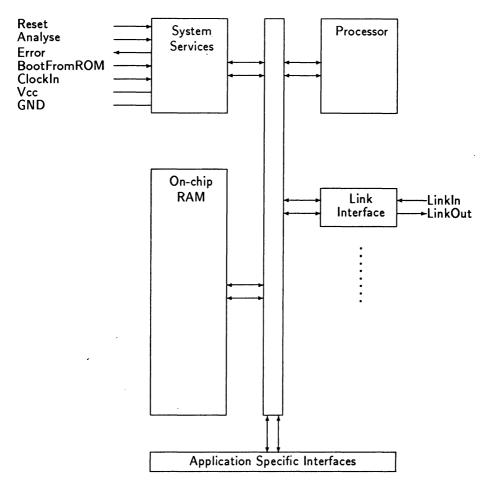

The transputer is a high performance microprocessor which has been designed to facilitate interprocess and interprocessor communication. The transputer architecture defines a family of programmable VLSI components which include the T212, T414 and a floating-point processor, the T800. In this text we shall only be considering the T414, but the general features of the transputer architecture are given in figure 2.1, and apply to the other members of the family. The principal features include:

- Processor

- On-chip static Random Access Memory (RAM)

- External memory controller

- Hardware time-slicing

- High-speed serial links (INMOS Links)

The T414 transputer is basically a 32-bit processor which has 2 Kbytes of static RAM and four communication links integrated onto a single chip in a CMOS process. Memory is extensible off chip with the total addressing range being 4 gigabytes  $(2^{32})$ . The data path to the memory is a full 32 bits wide, and configurable strobes are supplied that allow direct interfacing to dynamic RAM.

The processor itself is rated, for the standard 20 MHz part, at 10 MIPs (million instructions per second). The processor provides di-

Figure 2.1. Transputer architecture.

rect hardware support for the occam model of concurrency, with submicrosecond context switching, and two levels of process priority.

Communication with other processors or through link adaptor chips, to the outside world is provided by four independent, bi-directional IN-MOS serial links. These links run at bit rates of 5, 10 or 20 Mbps (million bits per second) and have DMA (Direct Memory Access) interfaces into memory to allow the transfer of messages to take place with the minimum of processor intervention. In addition, a single interrupt input, which is called the *event*, allows external circuitry to control a process.

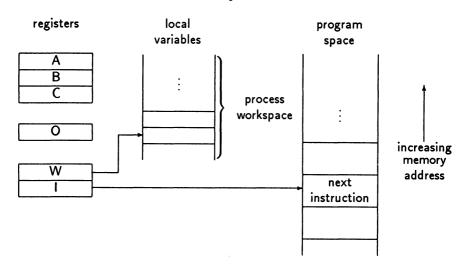

Figure 2.2. Transputer registers.

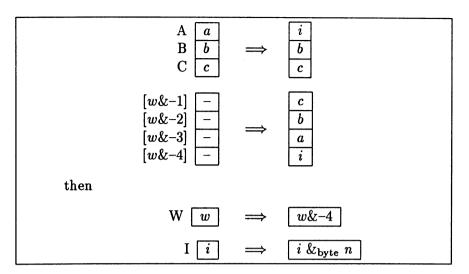

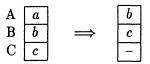

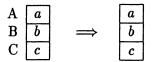

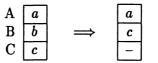

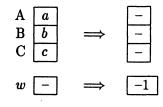

#### 2.2 Registers

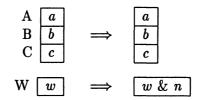

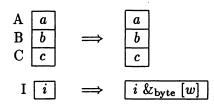

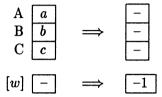

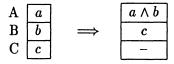

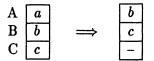

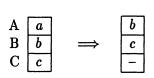

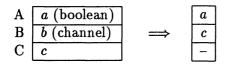

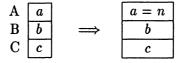

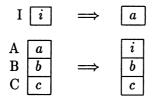

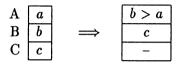

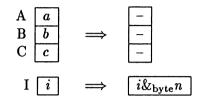

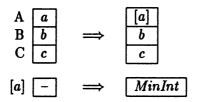

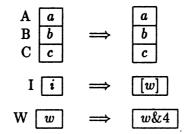

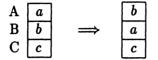

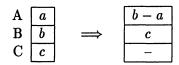

The transputer has a small register set as shown in figure 2.2, which consists of a workspace pointer W, an instruction pointer I, an operand register O, and three registers forming an evaluation stack: A, B and C. The workspace pointer points to an area of memory where local variables are held. The instruction pointer points to the next instruction to be executed. The operand register is used in the formation of instruction operands.

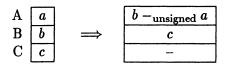

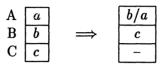

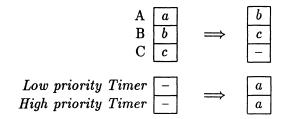

Registers A, B and C are sources and destinations for most arithmetic and logical operations. Loading a value onto the evaluation stack pushes B into C, and A into B, before loading A. Storing a value from A pops B into A and C into B. Expressions are evaluated on the evaluation stack, and instructions refer to the stack implicitly.

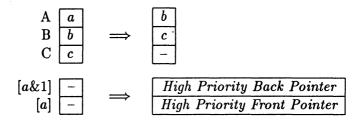

In addition to these six registers, there are four registers which handle the two active process queues, namely Fptr0, Fptr1, Bptr0 and Bptr1, and two timer registers Time0 and Time1. There are two single-bit flags for dealing with errors, Error and HaltOnError. In addition, the first few locations in internal memory are used for specific purposes.

The two timer registers Time0 and Time1 consist of a low priority timer which increments every 64 microseconds, and a high priority timer which increments every 1 microsecond. A single time slice lasts for 1024 high priority time periods, and low priority processes are descheduled at

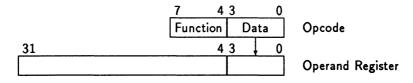

Figure 2.3. Instruction format.

the first opportunity after two time slice periods have been completed. High priority processes are never pre-empted.

When a process is timesliced out, the value of its instruction pointer I, is stored just below the current local workspace, i.e. one word below the address pointed to by the workspace pointer W. In addition, the process is linked to the back of the high or low priority active process queue. On the other hand, if a process becomes halted as a result of channel communication, then its instruction pointer is still stored, but in addition, its workspace pointer is placed in the word of memory allocated to the channel. When another process tries to communicate on the channel, i.e. attempts to access the channel word, the halted process is relinked to the back of the relevant active queue.

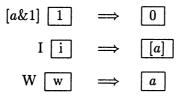

The instruction format of the transputer has been optimised for minimum code space requirements. Each instruction consists of a single 8bit byte which is split into two 4-bit values, making up a function and operand. This is shown in figure 2.3.

### 2.3 The Workspace Pointer

The workspace pointer holds an address. An address in general consists of two parts, a word selector and a byte offset within that word. The bottom few bits of the address form the byte offset, and the rest form the word selector. In the case of a 32-bit transputer such as a T414 or T800, two byte offset bits are used, allowing byte offsets 0,1,2 and 3.

The workspace pointer W is a one word wide register whose byte offset bits are set to zero, so that it always points to a word boundary in memory. The least significant bit is used instead to store the process priority, which is zero for a high priority process, and one for low priority. The combination of workspace address and priority bit is referred to as a *process descriptor*.

#### Chapter 2

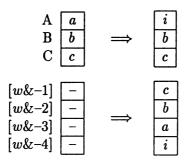

The workspace pointer points to the bottom of the workspace. It is used like a stack on a conventional processor to store return addresses and local variables during procedure calls. (Using conventional compiler terminology, we would say that the workspace pointer points to the base of the current stack frame.) This stack grows downwards towards more negative addresses, with local variables being accessed by positive offsets from W. As will be explained shortly, the way that transputer instructions are coded means that variables which are stored at small positive offsets from the workspace pointer can be accessed using very short instruction sequences.

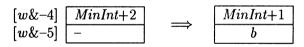

In addition, few words of memory just below the workspace pointer are used by the various parts of the scheduling hardware. In general, these are only used when the process is descheduled, so the value of the workspace pointer may be altered at any time by the programmer without harm being caused. The only exception to this is during the sequence of instructions that implements the selection part of an ALT construct, where W should be left undisturbed. The locations used are as follows, specified relative to W:

- -1 holds the instruction pointer of a descheduled process

- -2 used to maintain a list of active, but descheduled processes

- -3 used during channel communication to hold the address of data to be transferred

- -4 flag used during timer ALTs to indicate a valid time to wait for

- -5 used during timer ALTs to hold the time to wait for

Appendix C gives a more detailed description of the use of these locations, and shows what values each location may hold under various conditions.

## 2.4 The Instruction Pointer

The instruction pointer I, is the transputer's program counter. It points to the byte in memory that contains the next instruction to be executed. Instructions are actually read from memory a word at a time into an instruction pipeline buffer from where the processor takes them as required. This means that for a 32-bit processor, four instructions are read in a single cycle. On the T414, the pipeline can hold 8 instructions, that is two 32bit words. Since it takes no more than two memory cycles to fill, the number of memory cycles wasted by fetching unnecessary instructions when a branch is taken is only one, since one cycle is needed to fetch the branch instruction itself.

Unlike a conventional processor, the transputer has an instruction pointer value associated with each process. When a process is descheduled, this value is stored just below the current workspace, and when the process becomes the running process it is transferred back to the instruction pointer. As only one process can run at a time there needs to be only one instruction pointer register. The mechanism described enables the transputer to appear to run several processes simultaneously.

#### 2.5 The Operand Register

The operand register O, is a one word wide register which is used for assembling the operand of an instruction from the 4-bit data fragments supplied. All instructions place the contents of their 4-bit operand field into the least significant four bits of the operand register, moving the existing contents 4 bits to the left. The register is then used as the operand for the function which is specified by the other 4-bit field of the instruction.

Instructions normally clear the operand register after they have executed. However, a Prefix instruction exists which does nothing, except shift its four bits of operand left into the operand register, leaving this register uncleared after execution. Thus by using a series of Prefix instructions before a proper instruction, the range of that instruction's operand may be extended to as many bits as required. There is also a Negative Prefix instruction which complements the contents of the operand register after shifting.

Finally, there is an Operate instruction, which uses its operand as an opcode number, giving the transputer access to a further set of instructions above the basic 16 which are allowed for by the instruction format. Since the operand of the operate instruction may itself be extended by prefixing, the transputer can have an arbitrary number of instructions. The only proviso is that only 16 of them may actually have immediate operands (or 13, once Prefix, Negative Prefix and Operate are accounted for); the rest must have implicit operands. As an example, the ADD instruction adds the top two elements of the evaluation stack together,

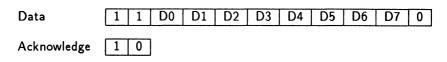

Figure 2.4. Link protocol.

leaving the result on the stack.

## 2.6 Communications Links

One of the aims of the transputer architecture is to provide a family of compatible components that can communicate with each other using the minimal amount of external logic, irrespective of the individual internal clock rates. To achieve this each transputer can communicate via point-to-point links called INMOS links, using an asynchronous bitserial protocol. Each transputer has a fixed number of such links, typically four; each of the links is bi-directional, and a variety of topologies can be configured using these links. For example, pairs of transputers may be connected together as a doublet, and then this doublet with its associated six links can be placed at each vertex of a cubic lattice.

The messages themselves are transmitted as a sequence of data packets, each of which must be acknowledged by an acknowledge packet. Each link consists of a pair of channels, one in each direction. Data packets for one direction are multiplexed on the same wire with acknowledge packets that are associated with messages for the other direction. The acknowledge packets are used both to signal reception of the data packets and to maintain flow control. The link protocol for the INMOS links is shown in figure 2.4. Transputer links themselves are formed by the interconnection of the *LinkIn* and *LinkOut* signals on the relevant transputers. Since the link protocol is asynchronous, the relative skew, which is typically caused by the different rising and falling edge times of the link signals, must be kept within tolerance. This needs careful consideration in its implication for certain interconnection topologies.

From the programmer's point of view there is no difference between sending a message between two processes running on separate transputers over a hardware link, and two processes running on the same transputer. In all cases, the programmer specifies an address in memory, called the channel word. Hardware determines whether the communication is internal or external, based on the address of the word. The conventional names and addresses for the channels associated with hardware links in the T414 are:

| PLACE | Link00utput | AT | #80000000: |

|-------|-------------|----|------------|

| PLACE | Link10utput | AT | #80000004: |

| PLACE | Link2Output | AT | #8000008:  |

| PLACE | Link30utput | AT | #8000000C: |

| PLACE | LinkOInput  | AT | #80000010: |

| PLACE | Link1Input  | AT | #80000014: |

| PLACE | Link2Input  | AT | #80000018: |

| PLACE | Link3Input  | AT | #8000001C: |

Each data packet as shown in figure 2.4 consists of a 'one' bit followed by another 'one' bit, followed by eight data bits followed by a zero bit. After transmitting a data packet, the sender transputer waits until an acknowledge is received, which signifies that the receiving transputer is ready to receive another packet. The acknowledge consists of two data bits, the first being a one and the second being a zero.

The receiving transputer can send an acknowledge as soon as the data packet has been identified, so that communications can be continuous, provided that there is sufficient buffer space for another data packet, and the inputting process is ready to receive the previous data packet. This protocol synchronises the communications of each byte of data. The communication is independent of word length, so that transputers using different word lengths can communicate directly.

Link selection pins on the transputer allow some selection of link speeds. Link speeds can be set by *LinkSpecial*, *LinkOSpecial* and *Link-123Special*. Link 0 can be set independently. In the table below, the values for the unidirectional and bidirectional data rates are given. *Linkn-Special* is to be taken as *LinkOSpecial* when selecting link 0 speed and as *Link123Special* for the others. All these rates are assuming that the transputer is using internal memory.

| Link-   | Linkn-  | Mbits/sec | Kbytes/se      | c (T414)      |

|---------|---------|-----------|----------------|---------------|

| Special | Special |           | unidirectional | bidirectional |

| 0       | 0       | 10        | 400            | 800           |

| 0       | 1       | 5         | 200            | 400           |

| 1       | 0       | 10        | 400            | 800           |

| 1       | 1       | 20        | 800            | 1600          |

#### Chapter 2

The INMOS links may be interfaced to peripherals via an INMOS link adapter, which converts a serial link into an 8-bit parallel port. Additionally, the transputer provides an input pin, *EventReq* and an output pin, *EventAck* which provide interrupt facilities. A peripheral may signal an interrupt to the transputer via the *EventReq* pin, which the transputer acknowledges using *EventAck*. Internally, the transputer makes available a special hardware channel which behaves as if a synchronising message has been received on each low to high transition of the *EventReq* pin. A process may wait on this 'channel', in which case it serves as an interrupt handler. An occam channel may be associated with the *EventReq* pin by a channel association. The conventional name and the address used for this channel are:

PLACE Event AT #80000020:

*Event* then behaves like an ordinary channel, and an occam process may synchronise with a low to high transition on the *EventReq* pin by using the occam construct

Event ? signal

The process then waits until the channel *Event* is ready. If the process waiting on the channel is high priority, then it will interrupt any low priority process running when *EventReq* goes from low to high.

## 2.7 Communication Protocol

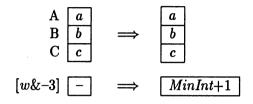

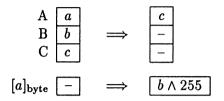

Communication over both internal and external channels is essentially byte orientated. The instructions concerned are IN, OUT, OUTWORD and OUTBYTE.

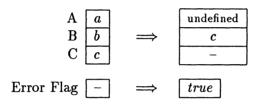

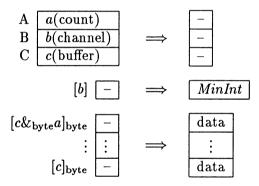

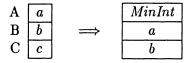

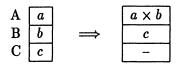

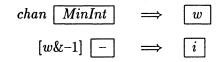

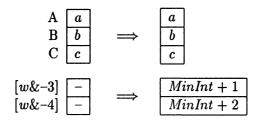

Communication over internal channels observes the following protocol. Before any communication is attempted, the channel word must be initialised to contain *MinInt*. This operation is done when the channel is declared and space is reserved for the channel word. When an input or output is subsequently attempted, the channel word is inspected: if it contains *MinInt*, then the process descriptor of the current process is placed in the channel word and the process is descheduled. In this case the instruction pointer and the address of the message to be transferred are stored at locations which have offsets of -1 and -3 relative to the workspace pointer, respectively. If however, the content of the channel word is not *MinInt*, thereby indicating that the other process involved is already waiting to communicate, then the communication may be performed.

The communication itself is achieved by copying the required block of data from the source to the destination. This is possible since the data address is available through the process descriptor stored in the channel word. Once the transfer is completed, the process that arrived first and was descheduled, is rescheduled and the channel word is reset to contain *MinInt*.

External links behave in a similar manner. The only difference as far as software is concerned is that the control word of an external link is at one of the addresses #80000000 to #8000001C rather than an arbitrary address in memory. The same instructions are used for input and output on both external links and internal channels.

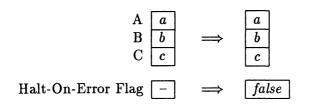

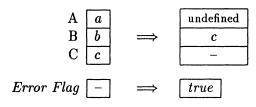

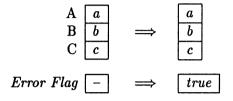

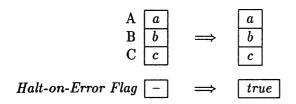

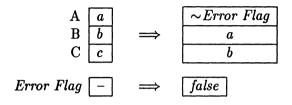

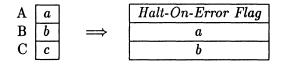

#### 2.8 Errors

High-level language execution is made secure with, for example, array bound checking and arithmetic overflow detection. If the compiler is unable to check that a given construct contains only valid expressions and processes, then extra instructions are compiled in order to perform the necessary check at runtime. If the result of this check indicates that an error has occurred then the processor's *Error* flag is set. This error can be handled either internally by software, or externally by using the *Error* pin. It is also possible, by setting the *HaltOnError* flag, to make the processor halt if the *Error* flag ever gets set. If the processor halts as a result of an error, then the links will continue with any outstanding transfers, the memory continues to provide refresh cycles and the transputer may be analysed.

When a high priority process pre-empts a low priority process then the status of the *Error* and *HaltOnError* Flags, and all the registers are saved in internal RAM in the area below *MemStart* for the duration of the high priority process, and restored at the conclusion of it. The status of the *Error* flag is transmitted to the high priority process, but the *HaltOnError* flag is cleared before the process starts. Either flag can be altered in the process without upsetting the error status of the preempted low priority process. When there are no high priority processes to run, then the current state of the *Error* flag is lost and the preserved state is restored, as part of commencing to execute the pre-empted low priority process. In the event of the transputer halting because of the *HaltOnError* flag, the links will finish outstanding transfers before shutting down. If the *Analyse* pin is asserted, then all inputs continue, but outputs will not make another access to memory for data.

After halting due to the *Error* flag becoming set whilst *HaltOnError* is set, the instruction pointer points to two bytes past the instruction which set the *Error* flag. After halting due to *Analyse* being taken high, the instruction pointer points one byte past the instruction which is being executed. In both of these cases the instruction pointer will be copied into the A register.

#### **2.9** Time

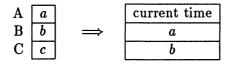

Timing in occam is provided by use of a timer channel which can only provide input. The value which is input is the current time, which is represented as an integer value. The cycle of the clock depends on the wordsize, on the amount by which the reading is incremented at each clock tick and on the frequency of the clock ticks. Each of these parameters will depend on the particular implementation of the hardware on which the occam program is running. In the transputer, the clock ticks for low priority processes are in units of (input clockrate)/(5\*64), which normally works out at 64 microseconds per tick. With a 64 microsecond tick and a 16-bit integer, then the cycle time would be approximately 4.2 seconds; with a 32-bit integer the corresponding cycle time would be approximately 76 hours.

The processor has timers to support two levels of priority. The priority 1 (low priority) processes are executed whenever there are no active priority 0 (high priority) processes. High priority processes are expected to execute for short time intervals. If one or more such processes can proceed, then one is selected and allowed to execute until it has to wait for a communication, a timer input, or until the process is completed. However, if no high priority process is able to proceed and one or more low priority processes are able to proceed, then one of the low priority processes is selected. Low priority processes are time-sliced to provide an even distribution of the processor time between computationally intensive tasks. If there are n low priority processes, then the maximum latency, expressed as the time from when a low priority process becomes active to the time at which it starts processing is (2n-2) time-slice periods. The low priority timer increments every 64 microseconds, whereas the high priority timer increments every 1 microsecond. A single timeslice period lasts for 1024 high priority time periods. In order to ensure that low priority processes do proceed, high priority processes must not continuously occupy the processor for a period equal to that of a time slice. If a low priority process is waiting for an external channel to become ready, and there are no active high priority processes, then the interrupt latency, which is the time interval from when the channel becomes ready until the process starts executing, is typically 19 processor cycles, though it may extend to a maximum of 58 cycles, all assuming the use of on-chip RAM.

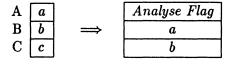

### 2.10 Reset, Analyse and Booting

The system services comprise the clocks, power and initialisation used by the whole of the transputer. The *Reset* and *Analyse* input pins enable the transputer to be initialised or halted in a way which preserves its state for subsequent analysis. While the transputer is running, both *Reset* and *Analyse* are held low. The transputer is initialised by pulsing *Reset* high whilst holding *Analyse* low. Operation ceases immediately and all current state information is lost. When *Reset* goes low the transputer sets up the memory interface configuration as appropriate. The processor and links start operating after the memory interface configuration cycle is complete and sufficient refresh cycles have been executed to initialise any dynamic RAM. The processor then bootstraps.

The transputer can be bootstrapped either from a link or from external ROM. If *BootFromRom* is connected high, then the transputer starts to execute code from the top two bytes in external memory, at address #7FFFFFE. This location should contain a backward jump to a program in ROM. The processor is in a low priority state. The workspace register points to *MemStart*, which is where the user memory begins and is at address location #80000048 for the T414.

If BootFromRom is connected low, the transputer will wait for the first bootstrap message to arrive on any one of its serial links. The transputer itself is ready to receive the first, or control byte, on the link within two processor cycles after *Reset* goes low. If the control byte received is greater than 1, then it is taken as the number of bytes to be input. The following bytes, up to this specified number, are then placed in internal memory starting at location *MemStart*. Following the receipt of the last byte, the transputer will start executing code at *MemStart* as a low priority process. The memory space immediately above the loaded code is used as workspace. Messages arriving on other links after the control byte has been received, or on the bootstrapping link after the last bootstrap byte, will be retained until a process inputs from the appropriate link.

The other options for the value of the control byte are 0 and 1, and use of these values allow the facility to 'peek' and 'poke'. Any location in either internal or external memory can be interrogated and altered when the transputer is waiting to boot from a link. If the control byte is 0 then eight more bytes are expected on the same link. The first 4 byte word is taken as an internal or external memory address at which to poke, i.e. write, the second 4 byte word. If the control byte is 1 the next four bytes are used as the address from which to peek, i.e. read, a word of data-this data word is sent down the output channel of the same link. After a peek or poke operation, the transputer returns to its previously held state. There is no limit to the number of peek and poke operations that may take place before the control byte has a value greater than 1, when the transputer will then begin to read its bootstrap code. When performing the peek and poke operations, any of the links may be used except that the addresses and data must be transmitted via the same link as that of the control byte.

When initialising after power-on, a time is specified during which the 5V supply, Vcc, must be within specification, *Reset* must be high, and the input on *ClockIn* must be oscillating. *Reset* is taken low after this specified time has elapsed.

In order to analyse a system following a reset, the first step is for the *Analyse* pin to be taken high. This causes the transputer to halt within three time-slice periods, approximately 3 milliseconds, plus the time taken for any high priority process to stop processing. Any outputting links continue to operate until they complete the remainder of the current word. Input links continue to receive data. Provided that there are no delays in sending acknowledgements, the links in the system will therefore cease activity within a few microseconds. Sufficient time must be allowed both for the processor to halt and for all the link traffic to be completed before *Reset* is asserted. The memory interface is not affected by *Analyse*, or *Reset* while *Analyse* is held high. If refresh cycles are enabled, then it continues to refresh external dynamic RAM.

After the end of a valid *reset* or *analyse* sequence, the processor's registers are initialised to specific values, depending on how the processor was started up. These values are as follows:

- W *MemStart* if bootstrapping from ROM, or the address of the first free word after a bootstrap program if bootstrapping from link.

- I MemStart if bootstrapping from a link, or the external memory bootstrap address (#7FFFFFE) if bootstrapping from ROM.

- A The value of I when the processor halted.

- **B** The value of W when the processor halted, together with the priority of the process when the transputer halted.

- C The identity of the bootstrapping link if bootstrapping from a link.

## Chapter 3

# **Instruction Set Overview**

The T414 has exactly one hundred instructions. These can be broken down as follows:

- 16 addressing and memory access,

- 41 arithmetic and logical,

- 6 branching and program control,

- 12 process scheduling and control,

- 16 inter-process communication,

- 9 miscellaneous.

It is interesting to note that instructions for dealing with concurrency amount to over a quarter of the total, or nearly five times the number of branching and program control instructions!

This chapter is designed to give an overview of the instruction set, with each instruction discussed within one of the groupings mentioned above. A more detailed explanation of each instruction will be found in the reference section of this book (Chapter 5).

## 3.1 Addressing and Memory Access

The transputer provides two main ways of addressing memory: addresses may be specified as a fixed offset from an address held in either the workspace pointer, or in the A register. The former is referred to as local access, since the workspace pointer conventionally points to an area of memory used to hold the local variables for a procedure. In fact, the first few words in memory offset from the workspace pointer are often referred to as 'local 0', 'local 1' etc. Conversely, access via the A register is called non-local.

Instructions are provided to read and write words from memory using the above addressing scheme; also provided are instructions to read and write bytes, to move a block of bytes, to perform word-length independent addressing calculations, to modify the value of the workspace pointer, and finally to specify an address relative to the instruction pointer.

## 3.1.1 Loading and Storing

The transputer provides the following general-purpose instructions for loading and storing words in memory:

| LDL n  | Load Local      |

|--------|-----------------|

| STLn   | Store Local     |

| LDNL n | Load Non-Local  |

| STNL n | Store Non-Local |

LDL n loads a word onto the evaluation stack (i.e. into the A register) which lies offset n words from the address pointed to by the workspace pointer, where n is the instruction's operand. The original value in A is pushed into B, and B into C. STL n performs the reverse, storing the value of the A register at the specified address. LDNL n and STNL n are similar, except that that they use the A register as the base address, rather than the workspace pointer. LDNL n loads the word into the A register, overwriting the address already stored there, while STNL n stores the value contained in the B register, afterwards popping both A and B.

| LDLP n  | Load Local Pointer     |

|---------|------------------------|

| LDNLP n | Load Non-Local Pointer |

are similar to the previous instructions, except that they store in A the effective address that is calculated, rather than the value of the word stored at that address. This is useful for subsequent instructions which require an address on the stack as one of their operands.

## 3.1.2 Byte Accesses

The transputer normally accesses memory a word at a time; however, it can be persuaded to access individual bytes with the next three instructions:

| LB   | Load Byte    |

|------|--------------|

| SB   | Store Byte   |

| MOVE | Move Message |

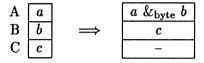

LB loads the byte at the address contained in the A register into the A register, overwriting its previous contents. Unlike word addressing, the bottom couple of bits of the address, which form the byte offset, are used to select a particular byte from within the word. SB stores a byte contained in the bottom eight bits of B at the address pointed to by A. Finally, MOVE copies a block of bytes from the address in C to the address in B, the number of bytes to move specified in A. The MOVE instruction is intelligent enough to read or write a word's worth of bytes in a single cycle wherever possible.

## 3.1.3 Addressing Arithmetic

The two instructions

| WSUB | Word Subscript |

|------|----------------|

| BSUB | Byte Subscript |

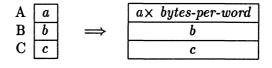

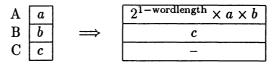

allow indexing of arrays, or their equivalents. WSUB increments the address in the A register by the number of words specified in the B register, whereas BSUB increments it by the number of bytes. The existence of these instructions allows address arithmetic to be word-length independent; for example on the T414, the returned value of WSUB is equivalent to a + 4b, while the T212 would return a + 2b.

Two further instructions,

| WCNT | Word Count |

|------|------------|

| BCNT | Byte Count |

are provided for word-length independent addressing. WCNT breaks the address in the A register into its word address and byte offset components, storing the two values in A and B, while BCNT multiplies the value in A by the number of bytes in a word. This would be useful in calculating the number of bytes in an array of words for a (byte oriented) MOVE command, for example.

#### 3.1.4 Other Addressing Instructions

There are two instructions that modify the value of the workspace pointer:

| AJW n | Adjust Workspace         |

|-------|--------------------------|

| GAJW  | General Adjust Workspace |

AJW n increments the workspace pointer by the number of words specified by its operand n (or decrements if n is negative). This instruction is most commonly used at the beginning and end of a procedure call, to allocate some more stack space and then relinquish it. Since the stack normally grows down in memory, the usual sequence of instructions would be AJW -k; ...; AJW +k, where k is the number of extra words to allocate.

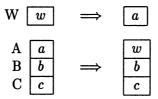

GAJW is a more general instruction, which simply exchanges the contents of the workspace pointer and the A register.

Finally, the instruction

#### LDPI Load Pointer To Instruction

calculates an address, which consists of the current value of the instruction pointer (which always points to the next instruction), incremented by the number of *bytes* specified by the value in the A register. This address then replaces the value in A. So, LDC 2; LDPI would leave an address in A which points two bytes on from the instruction following the LDPI. This is very useful for producing relocatable code, since a program's data can be specified relative to its code.

#### **3.2** Arithmetic and Logical

The three simplest instructions are

| REV   | Reverse         |

|-------|-----------------|

| LDC n | Load Constant   |

| MINT  | Minimum Integer |

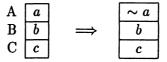

It could be argued that these are not really arithmetic instructions; however, this is the most convenient place to discuss them. REV simply swaps the contents of the top two elements of the evaluation stack, i.e. the A and B registers. LDC pushes the constant specified by its operand onto the evaluation stack, that is to say, storing it in the A register, pushing A onto B, B onto C, and losing the value in C. Finally, MINT pushes the constant *MinInt* onto the evaluation stack; this is a single-word value with the top bit set to 1 and all other bits to 0. This instruction is word-length independent. It is very useful, especially for channel communication (see later).

### 3.2.1 Single Length Arithmetic

Next there is the

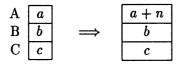

ADC n Add Constant

instruction, which adds its operand to the value in the A register, rather than just pushing it.

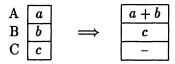

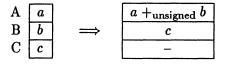

Then there are a group of eight arithmetic operators which take their operands from the A and B registers, leaving the result in the A register.

| Signed Addition    |

|--------------------|

| Signed Subtraction |

| Multiply           |

| Divide             |

| Remainder          |

|                    |

all perform signed single-length arithmetic, with the error flag being set on overflow, whereas

| SUM  | Unsigned Addition              |

|------|--------------------------------|

| DIFF | Unsigned Subtraction           |

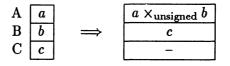

| PROD | <b>Unsigned Multiplication</b> |

are similar, except that carry and overflow are ignored. Finally,

FMUL Fractional Multiply

multiplies two single-word values together, but gives as its answer the high word of the result (more or less), rather than the low, as in MUL.

## 3.2.2 Comparing

There are two main comparison instructions.

EQC n Equals Constant

compares the value of the A register with the operand. If they are equal, true(1) is stored in A, else false (0) is stored.

#### GT Greater Than

compares the values in the A and B registers; if B is greater than A, then it returns *true* in the A register. Together with the logical/bitwise instructions discussed next, these two instructions can evaluate all the various types of arithmetic comparison. This is an example of where the transputer has the flavour of a RISC processor.

There are a further two comparison instructions which are designed mainly to check the range of array subscripts:

#### CSUB0 Check Subscript From Zero CCNT1 Check Count From One

Both these instructions check the range of the value in the B register, and if it is outside, set the error flag. The range is specified by the value of the A register; for CSUBO, the valid range is 0...a; for CCNT1, the valid range is 1...a.

### 3.2.3 Bit Operators

There are six bitwise operators.

| AND | Bitwise AND          |

|-----|----------------------|

| OR  | Bitwise OR           |

| XOR | Bitwise Exclusive-OR |

perform boolean operations between corresponding bits in the A and B registers.

NOT Complement

complements every bit in the A register, while

| SHL | Shift | Left  |

|-----|-------|-------|

| SHR | Shift | Right |

both shift the value in the B register left or right by the number of places specified by the A register, filling the extra bits with zeros.

#### 3.2.4 Multiple Word Arithmetic

There are versions of most of the above arithmetic instructions designed to deal with multiple word-length data.

| LADD  | Long Add        |

|-------|-----------------|

| LSUM  | Long Sum        |

| LSUB  | Long Subtract   |

| LDIFF | Long Difference |

have the same effect as their single-word counterparts, except that a single bit carry or borrow is contained in the C register. LSUM and LDIFF are used for the low order words of the calculation, while LADD and LSUB are used for the top word, since they perform overflow checking.

LMUL Long Multiply

multiplies the values in the A and B registers together and adds in the 'carry' in the C register. The double word result is stored in the A and B registers, the high word in B. The value in B thus becomes the carry-in for higher order words.

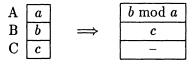

LDIV Long Divide

divides the double-length word in register pair BA by the value in C, storing the integer result in A and the remainder in B. Note that to avoid overflow, B must be less than C.

The two instructions

| LSHL | Long Shift | Left  |

|------|------------|-------|

| LSHR | Long Shift | Right |

shift the double word value contained in register pair BA a number of places specified by the C register, filling the extra bits with zeros.

Finally,

| XDBLE | Extend To Double |

|-------|------------------|

| CSNGL | Check Single     |

convert a single word value into a double word value and vice versa. CSNGL sets the error flag if the value cannot be squeezed into a single word.

## 3.2.5 Partword Arithmetic

Partword arithmetic (that is to say, using signed numbers represented by less bits than there are in a word) is supported by the two instructions

| XWORD | Extend To Word |

|-------|----------------|

| CWORD | Check Word.    |

The idea is that partword values are first sign-extended to full words using XWORD; normal arithmetic operations are then carried out, and the result is checked with CWORD, which sets the error flag if the value is out of the partword range.

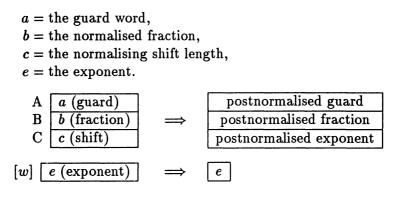

## 3.2.6 Floating-Point Support

The instruction

NORM Normalise

normalises the double word value in BA by shifting it left until the top bit is set. The number of places shifted left is stored in C.

There are a further set of instructions

| CFLERR     | Check Floating Point Infinity or Not-a-Number |

|------------|-----------------------------------------------|

| LDINF      | Load Single Length Infinity                   |

| POSTNORMSN | Post-Normalise Correction                     |

| ROUNDSN    | Round Single Length Floating Point Number     |

| UNPACKSN   | Unpack Single Length Floating Point Number    |

which are specific to the T414, and are designed to provide hardware support for (software) floating-point packages. For obvious reasons they have not been included in the floating-point T800 transputer. Incidentally, it is the existence of these instructions that gives the T414 a floating-point performance which is comparable to processors with dedicated floating-point co-processors (such as the 68020/68881 combination).

## 3.3 Branching and Program Control

The transputer provides only six instructions for altering the flow of control of the program. In this respect, it again comes close to being a RISC processor.

#### 3.3.1 Branching

The three instructions

| CJn  | Conditional Jump |

|------|------------------|

| Jn   | Jump             |

| LEND | Loop End         |

provide branching. CJ n examines the value in the A register. If it is *false* (0), then the instruction pointer is incremented by the number of bytes specified by n, causing a branch. If A is non-zero, then no branch is taken, but the value in A is popped. J n is similar, except that it is unconditional.

LEND is designed to implement deterministic loops. It takes two parameters: in A there is a displacement which is to be subtracted from the instruction pointer should the instruction succeed; in the B register, there is a pointer to a two-word control block. Each time the instruction is executed, the value of the first word is incremented, and the second decremented. If the value remaining in the second word is greater than zero, the branch is taken, using the offset specified in the A register. Note that the value in A specifies how many bytes to go back by.

As an example, the Pascal code FOR i := 3 TO 8 DO

```

j := j + i;

would be implemented as

LDC 3; STL block;

LDC 8-3+1; STL block+1;

L1: LDL j; LDL block; ADD; STL j;

LDLP block;

LDC L2-L1;

LEND;

L2:

```

The two instructions J and LEND provide the points where the transputer may time-slice between low priority processes. Consequently, if a section of code does not make use of these two (for example, it uses CJ instead), then the process will never be time-sliced out, unless pre-empted by a high priority process.

## 3.3.2 Subroutine Calling

The remaining three instructions are designed to implement procedure calls.

| CALL n | Call         |

|--------|--------------|

| RET    | Return       |

| GCALL  | General Call |

CALL n decrements the workspace pointer by four bytes, stores at the four words thus allocated (in descending order) the current contents of the C, B, A and instruction pointer registers and then increments the instruction pointer by the number of bytes specified by the operand n. It thus implements a relative call instruction. RET loads the instruction pointer with the value pointed to by the workspace pointer, and increments the workspace pointer by four words. Thus RET will always return from a CALL as long as the workspace pointer remains unchanged.

If this procedure call mechanism is found to be too restricting, a more general one may be implemented using GCALL, which just exchanges the contents of the A register and the instruction pointer. It is then up to the programmer to sort out such things as storing the return address and so on.

## **3.4** Process Scheduling and Control

#### 3.4.1 Background

The transputer has built-in mechanisms to support the concurrent execution of processes. Processes may be operated at two levels of priority. Two queues of active processes are maintained, one for high, and one for low priority processes. A process can be in one of four states: executing; waiting to execute, which implies that it is in one of the active process queues; waiting for a timer event, which implies that it is in a timer queue, or waiting for a communication event, in which case it is in no queue.

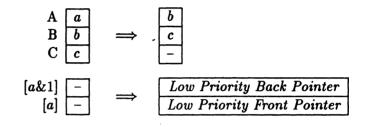

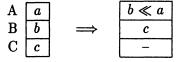

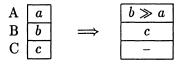

A high priority process will execute without interruption until it terminates, or waits for a timer or communication event to take place. In this case, if there are any further high priority processes waiting to proceed then the process at the head of the high priority active process queue will be scheduled. If there are no high priority processes waiting to execute, then the next waiting low priority process will be scheduled. Low priority processes may be pre-empted at any time by a high priority process that becomes ready to execute. Low priority processes are time-sliced; if a low priority process executes a Jump or Loop End instruction, and has been executing for more than its time-slice period, it is descheduled and placed at the back of the low priority active queue, with the process at the head of the queue commencing execution.

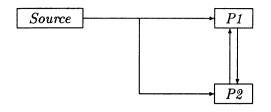

#### 3.4.2 Start Process and End Process

The transputer provides five instructions to allow the setting up of new processes, and the killing off of others. Two of the instructions are designed to directly support the occam view of concurrency, or more specifically, the occam PAR construct. In the occam program shown in figure 3.1, section P is executed first, and then (conceptually, at least), the current process is suspended, and three new processes are started which execute sections Q, R and S in parallel. Only when all three of these child processes have successfully terminated, is the parent process rescheduled, which then executes section T. If any of the children fail to terminate successfully, then the parent process will never be rescheduled.

The way that an occam compiler would treat the above code is in fact slightly different from that just described. Only two child processes would be set up, with the parent process taking over the execution of section S. The first two of the three processes to finish their section of

```

SEQ

section P

PAR

section Q

section R

section S

section T

```

Figure 3.1. An occam PAR construct.

code just terminate, while the last one to terminate resumes execution of section T.

The two instructions

| STARTP | Start Process |

|--------|---------------|

| ENDP   | End Process   |

are designed specifically to implement this scheme. STARTP adds a new process to the back of the active process queue. It takes two parameters: the A register holds the address of the workspace that the new process will use, and B holds an offset in bytes from the current instruction (or more accurately, the next instruction) to the section of code that the new process is to execute. The new process is set at the same priority as the current process, and the current process continues execution with the next instruction. Note that the new execution address is specified relative to the old, following the usual transputer philosophy that code produced should be relocatable, unless the programmer tries very hard to do otherwise!

ENDP is designed to conditionally terminate a process. What it does is to decrement a count somewhere in memory. If this count is non-zero then it just terminates, that is to say, the next active process is taken from the queue and executed, and the current process is *not* added to the back of the queue. If on the other hand the count has reached zero, then the process continues, but at a different execution address, and with a different workspace pointer. More precisely, the instruction takes one parameter, an address in the A register. This address points to the workspace of the parent process. At location 0 in this workspace is the restart address of the parent process (in the example above this is the address of code section T). Location 1 holds the count of child processes. If the instruction decrements this value to zero, it sets its workspace pointer to the value in the A register, and its instruction

|                 | workspace    |                   | workspace   |

|-----------------|--------------|-------------------|-------------|

|                 | for sections |                   | for section |

| $W \rightarrow$ | P and T      | $W_s \rightarrow$ | S           |

|                 | (swap)       |                   | (swap)      |

|                 |              |                   | workspace   |

|                 |              |                   | for section |

|                 |              | $W_q \rightarrow$ | Q           |

|                 |              |                   | (swap)      |

|                 |              |                   | workspace   |

|                 |              |                   | for section |

|                 |              | $W_r \rightarrow$ | R           |

|                 |              |                   | (swap)      |

|                 |              |                   |             |

Figure 3.2. Workspaces for the PAR processes.

pointer to the value pointed to by A.

The PAR construct above would thus be executed as follows: the parent process, after having executed section P, stores the count three at local 1, and the address of the code for section T at local 0. It then executes two STARTP instructions, which set up processes to execute sections Q and R. It then performs a jump to section S.

At this point, there are three concurrent processes, executing sections Q, R and S. The first two of these processes to finish will terminate after decrementing the count. The last to terminate will then 'assume the role' of the parent process, executing section T.

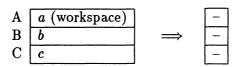

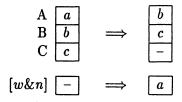

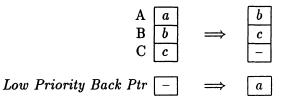

Note that in occam, the compiler can determine at compile time the workspace requirements for each process. Thus it can allocate workspaces for Q and R at fixed positions below the workspace for the parent process. This is shown in figure 3.2. The figure on the left indicates the state of the workspace when there is only the single process running. The workspace pointer W points to the base of the workspace (i.e. location 0) of the process that executes section P and T.

A couple of words below the workspace are reserved for use by the scheduling hardware should the process be descheduled. (Note that this would be more, up to five words, if channel communication or timer ALTs are used by the process—see the next section for details.) The

```

P: {section P}

LDC 3; STL 1;

LDC (T-LO); LDPI

LO: STL 0:

LDC (R-L1); LDLP -(q+2)-(r+2); STARTP;

L1: LDC (Q-L2); LDLP -(q+2);

STARTP:

L2: J (S-Q)

{section Q}

O:

LDLP (q+2);

ENDP:

{section R}

R:

LDLP (q+2)+(r+2); ENDP;

{section S}

S:

LDLP 0;

ENDP;

T: {section T}

```

Figure 3.3. Code for a PAR construct.

second diagram shows the situation after the PAR section has been entered. The original process carrys on using the same workspace (which is assumed to be large enough to hold the local variables for P, T and S, while the two new processes are allocated new workspaces below the original.

Thus the code for the example above may be coded as in figure 3.3. Here, q and r are the sizes of workspace required for Q and R.

If it is not possible to determine at compile time the address of the original workspace relative to each of the children, then one possibility is that the address of the parent workspace be stored at the first location (say) of each of the child processes when they are being set up. Then the above code would be changed to look like that in figure 3.4.

Note that if any of the processes executing sections Q, R and S hang (for example if they execute Stop On Error after an error—see below), then no process will ever proceed to execute section T. Thus, if the section of occam program given above is itself part of a family of PAR processes, then that family's parent will eventually hang, and so on.

#### 3.4.3 Other Process Instructions

There are three other instructions which initiate and terminate processes:

```

P: {section P}

LDC 3; STL 1;

LDC (T-LO); LDPI

LO: STL 0;

LDLP 0:

STL -(q+2)-(r+2);

LDC (R-L1); LDLP -(q+2)-(r+2); STARTP;

LDLP 0;

STL -(q+2);

L1: LDC (Q-L2); LDLP -(q+2);

STARTP:

L2: J (S-Q)

Q:

{section Q}

LDL O; ENDP;

{section R}

R:

LDL O: ENDP:

S:

{section S}

LDLP O; ENDP;

{section T}

Т:

```

Figure 3.4. Modified code for a PAR construct.

| STOPP   | Stop Process  |

|---------|---------------|

| STOPERR | Stop On Error |

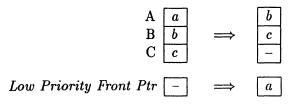

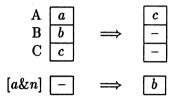

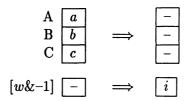

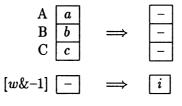

| RUNP    | Run Process   |