# TRANSPUTER INSTRUCTION SET

a compiler writer's guide

**INMOS Limited**

**Prentice Hall**

New York London Toronto Sydney Tokyo Singapore

First published 1988 by Prentice Hall International (UK) Ltd, 66 Wood Lane End, Hemel Hempstead, Hertfordshire, HP2 4RG A division of Simon & Schuster International Group

**1**

#### © 1988 INMOS Limited

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate, however no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

, inmos, IMS and OCCam are trademarks of the INMOS Group of Companies.

INMOS document number: 72 TRN 119 05

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission, in writing, from the publisher. For permission within the United States of America contact Prentice Hall Inc., Englewood Cliffs, NJ 07632.

Printed and bound in Great Britain at the University Press, Cambridge

CIP data are available

3 4 5 6 93 92 91 90

8-001PSP-E1-0 NBZI

# Contents

|   | Prefa          | Preface Introduction                     |    |  |  |  |  |  |  |

|---|----------------|------------------------------------------|----|--|--|--|--|--|--|

| 1 | Introd         |                                          |    |  |  |  |  |  |  |

| 2 | Basic concepts |                                          |    |  |  |  |  |  |  |

|   | 2.1            | The transputer instruction set           | 3  |  |  |  |  |  |  |

|   | 2.2            | Occam processes                          | 3  |  |  |  |  |  |  |

|   | 2.3            | Process scheduling                       | 3  |  |  |  |  |  |  |

|   | 2.4            | Inter-process communication              | 4  |  |  |  |  |  |  |

| 3 | Wordl          | 5                                        |    |  |  |  |  |  |  |

|   | 3.1            | Wordlength and addressing 3.1 Addressing |    |  |  |  |  |  |  |

|   | 3.2            | Byte addressing                          | 6  |  |  |  |  |  |  |

| 4 | Instru         | action representation                    | 7  |  |  |  |  |  |  |

|   | 4.1            | Direct functions                         | 7  |  |  |  |  |  |  |

|   | 4.2            | Prefix functions                         | 7  |  |  |  |  |  |  |

|   | 4.3            | Indirect function                        | 7  |  |  |  |  |  |  |

|   | 4.4            | Generating prefix sequences              | 8  |  |  |  |  |  |  |

| 5 | Seque          | ential processes                         | 11 |  |  |  |  |  |  |

|   | 5.1            | Registers                                | 11 |  |  |  |  |  |  |

|   | 5.2            | Local variables and constants            | 12 |  |  |  |  |  |  |

|   | 5.3            | Expression evaluation                    | 12 |  |  |  |  |  |  |

|   | 5.4            | Arrays and subscripts                    | 17 |  |  |  |  |  |  |

|   | 5.5            | Assignment                               | 21 |  |  |  |  |  |  |

|   | 5.6            | Comparisons and conditional behaviour    | 22 |  |  |  |  |  |  |

|   | 5.7            | Long arithmetic and shifts               | 26 |  |  |  |  |  |  |

|   | 5.8            | Integer length conversion                | 29 |  |  |  |  |  |  |

|   | 5.9            | Replication                              | 30 |  |  |  |  |  |  |

|   | 5.10           | Procedures                               | 31 |  |  |  |  |  |  |

|   | 5.11           | Functions                                | 35 |  |  |  |  |  |  |

|   | 5.12           | Error handling                           | 36 |  |  |  |  |  |  |

|   | 5.13           | Additional instructions                  | 38 |  |  |  |  |  |  |

| 6 | Concu          | urrent processes                         | 39 |  |  |  |  |  |  |

|   | 6.1            | Workspace                                | 39 |  |  |  |  |  |  |

|   | 6.2            | Process descriptors                      | 39 |  |  |  |  |  |  |

|   | 6.3            | Scheduling and priority                  | 40 |  |  |  |  |  |  |

|   | 6.4            | Initiation and termination               | 41 |  |  |  |  |  |  |

|   | 6.5            | Compiling PAR                            | 42 |  |  |  |  |  |  |

|   | 6.6            | Other scheduling instructions            | 42 |  |  |  |  |  |  |

|   | 6.7            | PRI PAR                                  | 43 |  |  |  |  |  |  |

|   | 6.8            | Channels and communication               | 43 |  |  |  |  |  |  |

|   | 6.9            | Time                                     | 44 |  |  |  |  |  |  |

|   | 6.10           | Alternative input                        | 45 |  |  |  |  |  |  |

| 7  | Floati | ing point arithmetic                      | 49 |

|----|--------|-------------------------------------------|----|

|    | 7.1    | Overview of the IMS T800                  | 49 |

|    | 7.2    | Registers                                 | 50 |

|    | 7.3    | Loading floating point values             | 51 |

| -  | 7.4    | Storing values                            | 52 |

|    | 7.5    | Expressions                               | 53 |

|    | 7.6    | Comparisons                               | 57 |

|    | 7.7    | Class analysis                            | 58 |

|    | 7.8    | Floating point error handling             | 59 |

| -  | 7.9    | Type conversion                           | 62 |

|    | 7.10   | Saving the floating point unit state      | 64 |

|    | 7.11   | Floating point support for IMS T414       | 65 |

|    | 7.12   | Implementing floating point arithmetic    | 66 |

| 8  | Speci  | alist instructions                        | 67 |

|    | 8.1    | Two dimensional block move                | 67 |

|    | 8.2    | Bit manipulation and CRC evaluation       | 68 |

|    | 8.3    | Resetting a channel                       | 69 |

| 9  | Roots  | strapping and analysing                   | 73 |

|    | 9.1    | Resetting and analysing                   | 73 |

|    | 9.2    | Reset and power up                        | 73 |

|    | 9.3    | Analyse                                   | 76 |

|    | 9.4    | Error detection by hardware               | 77 |

|    | 9.5    | The register save area                    | 79 |

| 10 | Archit | tectural details                          | 81 |

|    | 10.1   | Process scheduling queues and timer lists | 81 |

|    | 10.2   | Special RAM locations                     | 83 |

|    | 10.3   | Special workspace locations               | 84 |

|    | 10.4   | Channel communication                     | 85 |

|    | 10.5   | Execution of an ALT construct             | 87 |

|    | 10.6   | CPU/FPU interface                         | 88 |

|    | 10.0   | OF OFFI O INTO THE OFFI                   |    |

| 11 | Hints  | and tricks                                | 91 |

|    | 11.1   | Optimising use of on-chip RAM             | 91 |

|    | 11.2   | Tables of constants                       | 92 |

|    | 11.3   | Implementing the occam error modes        | 92 |

|    | 11 4   | Optimising floating point performance     | 95 |

|   | Appe   | ndices                                                 | 101 |

|---|--------|--------------------------------------------------------|-----|

| A | IEEE   | floating point format                                  | 103 |

|   |        |                                                        |     |

| В | Comp   | 105                                                    |     |

|   | B.1    | The IEEE standard and INMOS implementations            | 105 |

|   | B.2    | IMS T800                                               | 105 |

|   | B.3    | Software implementations                               | 107 |

|   | B.4    | Error flagging software implementations                | 109 |

|   | B.5    | Full IEEE arithmetic                                   | 110 |

|   | B.6    | Not-a-Number values                                    | 110 |

| С | Speci  | al values                                              | 113 |

| D | Inetru | ictions set summary                                    | 115 |

|   | D.1    | Direct, prefixing and indirect functions               | 116 |

|   | D.2    | Operations                                             | 117 |

|   | D.3    | Extra instructions on 32 bit transputers               | 119 |

|   | D.4    | Extra instructions on IMS T414                         | 119 |

|   | D.5    | Additional instructions on IMS T800                    | 120 |

| E | Instru | actions set reference                                  | 123 |

|   | E.1    | Direct functions                                       | 123 |

|   | E.2    | Operations                                             | 124 |

| F | Speci  | fication of instruction set                            | 127 |

|   | F.1    | Definitions                                            | 127 |

|   | F.2    | Reading a specification                                | 128 |

|   | F.3    | Instruction specifications                             | 132 |

|   | F.4    | Additional non floating point instructions on IMS T800 | 147 |

| G | Speci  | fication of floating point unit instructions           | 149 |

|   | G.1    | Datatypes                                              | 149 |

|   | G.2    | Floating point unit state                              | 150 |

|   | G.3    | Floating point unit entry                              | 150 |

|   | G.4    | Floating point unit operations                         | 150 |

|   | Instru | ction index                                            | 162 |

|   | 1      |                                                        | 101 |

|   | Index  |                                                        | 164 |

# **Preface**

This book is the guide to the instruction set of the transputer family. A transputer is a single VLSI device with processor, memory and communication links for direct connection to other transputers. Transputers are designed to allow parallel systems to be built from collections of processors operating concurrently and communicating through links.

Although this book is the transputer instruction set definition and is intended to be a reference manual for programmers it is not set out in the 'traditional' form. This has been done quite deliberately. A traditional instruction set document contains brief descriptions of the individual instructions one by one — probably in alphabetic order of mnemonics — along with tables detailing the addressing modes available and the effects of the instruction on various flags, memory, registers etc. The more traditional form of document provides all the information about the instruction set — but leaves the reader to find out how best to use it. This was (perhaps) appropriate when the bulk of programming was being performed in assembly language. However when writing this book the following assumptions have been made

- 1. Assembly language programming lacks security.

- Concurrent assembly language programming is even harder than traditional assembly language programming.

- A language like occam provides a means for writing efficient concurrent programs for transputers as well as permitting formal verification through proof techniques.

- 4. Current compiler techniques, along with a well designed language and instruction set can provide high level language performance comparable to assembly language. In fact compiled code can often have higher performance as a compiler can automatically perform optimisations such as the use of constant tables, case selection jump tables and re-ordering of expression evaluation — techniques for all of these are included.

For these reasons this book introduces the transputer instruction set in terms of compiler writing. The intention is that programs for transputers are compiled from high level languages — such as occam, C, Fortran, Modula-2 etc. — into transputer code rather than being written at the assembly language level. Instructions are introduced to explain the compilation of various aspects of a high level language. The compilation of constructs of a high level language is given in terms of translations from occam code to sequences of transputer instructions. Algorithms suitable for implementation in a compiler are given for various constructs where careful choice of the compiled code can increase performance.

The high level programming language examples used in this book are in occam 2. Further details of this language can be found in the *occam 2 Reference Manual*. Compilation strategies for other languages can be developed by looking at the compilation of similar constructs in occam.

# 1 Introduction

This guide explains how high level programming language constructs can be translated into sequences of transputer instructions. It is assumed that a compiler for a language other than occam will translate a program into an occam like process, communicating with other processes only via occam channels. In this way, it is possible to freely mix languages in a system. In particular, occam can be used as a system description and configuration language, with other languages being used to write individual processes within the system.

The guide deals with various high level language constructs individually. Transputer instructions are introduced as they are needed in the implementation of these constructs. The instructions are normally explained when they are first introduced but in some cases this is delayed until a later section which is more appropriate.

#### Undefined values

In the definition of many instructions the values left in certain registers are said to be undefined. This should be taken as meaning that those values are not defined by INMOS and that INMOS does not claim that future transputers will behave in the same way as current transputers. No application should ever attempt to make use of the value that the current transputer implementations happen to provide in such cases.

# Program notation

The language occam is used in this book both as a 'source language' to represent program constructs and program fragments to be compiled, and as a 'meta-language' to represent algorithms to produce compiled code and other examples. These two uses of occam will be distinguished by the use of an italic font for meta-language occam as in

$$x := a + b$$

and a teletype font for source language occam as in

$$x := a + b$$

Inside source language occam an italic font is used for 'meta-variables'. For example

PAR P O

represents any two processes P and Q in a parallel construct.

The source language occam is the occam 2 language as defined in the *occam 2 Reference Manual*. The meta-language occam is based on occam 2 with some restrictions removed and extensions added to enable certain algorithms to be expressed more simply.

2 1 Introduction

# 2 Basic concepts

# 2.1 The transputer instruction set

The instruction set is designed for simple and efficient compilation. All instructions have the same format, which is chosen to give a compact representation of the operations most frequently occurring in programs. Instructions are independent of the processor word-length, which may be any number of bytes. (The same instruction set could be used for a 16, 24 or 32 bit processor).

Enhanced versions of transputers provide added features — such as full hardware support of floating point arithmetic — so certain sections of this guide will be specific to transputers with those enhancements. This will be noted where appropriate.

# 2.2 Occam processes

A process starts, performs a number of actions, and then either stops or terminates successfully. Each action is either an assignment, an input or an output. An assignment sets the value of a variable, an input receives a value from a channel, and an output sends a value to a channel. The variable set by an assignment should not be accessible to any other process — the only method of transferring information from one process to another should be by using a channel.

At any time between it starting and terminating successfully a process may be ready to communicate on one or more of its channels. Each channel provides one way communication between two processes.

Communication is synchronised. If a channel is used for input in one process and output in another then communication takes place when both processes are ready. The inputting and outputting processes then proceed with the value output being copied from the outputting process to the inputting process.

Externally a process may be seen as being a 'black box' that, after starting, may or may not wish to communicate along one or more of its channels until it terminates successfully. A correctly functioning process will normally communicate data with the processes connected to it to perform the task it is designed to achieve, and then terminate successfully. However, a process can fail to communicate indefinitely. This failure of communication can be due to internal deadlock (where all internal processes are waiting to communicate with each other), internal livelock (where internal processes are only communicating with themselves and will never communicate with the outside world) or due to the process ceasing to execute without terminating successfully (in occam this is the STOP process).

The internal state of a process is not visible to the outside world and all interactions with the process occur via channel communication. This process model removes the problems associated with variable sharing. Also if a process is re-implemented to have the same behaviour and channel interface it can be immediately substituted in a system allowing for prototypes to be refined in stages into more efficient implementations.

# 2.3 Process scheduling

Each transputer executes an occam process. This process may itself consist of a number of concurrent processes. Concurrent processing within a transputer is implemented by sharing the processor time between the concurrent processes.

The processor executes one process at a time. The process being executed is called the current process, and the set of processes which are ready for execution is called the active set.

The processor can execute a process at one of two priority levels — level 0 for urgent processes and level 1 for less urgent processes. The processor will execute a level 0 process in preference to a level 1 process

4 2 Basic concepts

if both are active, so that the level 1 process will be interrupted.

The current process is executed until it is unable to proceed because it is waiting to input or output, waiting for the timer or it has been interrupted by a higher priority process. In addition time is shared between level 1 processes by timeslicing so that a level 1 process will suspend its execution after certain instructions if it has been scheduled for more than a timeslice period. When the current process is unable to proceed, a new current process is taken from the active set. An interrupted process is resumed as soon as all higher priority processes become unable to proceed.

# 2.4 Inter-process communication

Communication between processes is achieved by the use of channels. Channels between processes in the same transputer are implemented using memory locations, and channels between processes in different transputers are implemented by point-to-point links. Each link between two transputers is used solely for communication between those two transputers, and provides one occam channel in each direction.

A process can be written and compiled without knowledge of whether its channels are connected to other processes on the same transputer, or on another transputer. The same instruction sequence is used in both cases.

As in the occam model, communication takes place when both the inputting and outputting processes are ready. Consequently, the process which first becomes ready must wait until the second one is also ready. The first process is removed from the active set and its identity is stored in the channel. The processor starts to execute the next process from the active set. When the second process becomes ready, the message is transferred, and the waiting process is returned to the active set.

# 3 Wordlength and addressing

The instruction set is independent of the processor wordlength. Programs which manipulate bytes, words and truth values can be translated into an instruction sequence which behaves identically whatever the wordlength of the processor executing it. This results from the design of the memory addressing instructions, the use of single byte instructions, and the method of representing long operands as a sequence of prefix instructions. Differences in behaviour will come from the different word size used for arithmetic, which may result in differing overflow behaviour, and also from byte access to word arrays.

If compilers are written to produce code that does not explicitly use information about the wordlength, number of bytes per word etc., then retargetting to a transputer of a different wordlength will be much simpler. It is possible to generate code that will run on any current transputer, enabling networks of various transputers to be used without prior knowledge of their wordlengths.

# 3.1 Addressing

A pointer is a single word of data which identifies a byte in memory.

#### 3.1.1 Word address and byte selector

A pointer is divided into two parts, a word address and a byte selector. The byte selector occupies the least significant bits of the word; the word address the most significant bits. The number of bits needed to represent the byte selector depends on the wordlength. (For example, 1 bit for a 16 bit machine, 2 bits for 24 or 32 bit machines, 4 bits for an 80 bit machine). The pointer is treated as a signed value with pointer values starting from the most negative integer and continuing, through zero, to the most positive integer. This enables the standard comparison functions to be used on pointer values in the same way that they are used on numerical values. Of course, if the number of bytes in a word is a power of two, the addresses are consecutive and normal arithmetic can also be used on pointers.

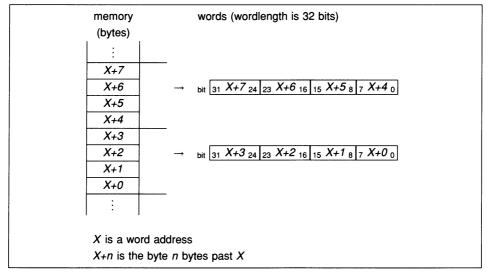

Figure 3.1 Bytes in memory and words

Certain values are never used as pointers, and are used in the implementation of communication and scheduling. These values correspond to the most negative pointer values.

In the following description, names are used to represent these and other values as follows

MostNeg the most negative value (the most significant bit is one, and all other bits

are zero)

MostPos the most positive value (the most significant bit is zero, and all other bits

are one)

NotProcess.p (= MostNeg) — used for communication and scheduling

# 3.2 Byte addressing

The transputer is totally 'little-endian' — i.e. less significant data is always held in lower addresses. This applies to bits in bytes, bytes in words and words in memory. Hence, in a word of data, one byte is more significant than another if its byte selector is the larger of the two. Figure 3.1 shows the ordering of bytes in words and memory for a 32 bit transputer.

# 4 Instruction representation

Each instruction is one byte long, and is divided into two 4 bit parts. The four most significant bits of the byte are a function code, and the four least significant bits are a data value.

The representation provides for sixteen functions, each with a data value ranging from 0 to 15.

## 4.1 Direct functions

Research has shown that computers spend most of the time executing instructions to load and store from a small number of 'local' variables, add and compare with small constants, and jump to or call other parts of the program.

Thirteen of the functions are used to encode the most important operations performed by any computer executing a high level language. They include jumps, calls and the instructions used to access variables.

#### 4.2 Prefix functions

Two more functions are used to allow the operand of any instruction to be extended in length.

pfix prefix

nfix negative prefix

All instructions begin by loading the four data bits of the instruction into the least significant four bits of the operand register which is then used as the operand of the instruction. All instructions except the prefix instructions end by clearing the operand register, ready for the next instruction.

The *pfix* instruction loads its four data bits into the operand register, and then shifts the operand register up four places. The *nfix* instruction is similar, except that it compliments the operand register before shifting it up. Consequently, a sequence of one or more prefix instructions can be placed before any instruction to extend its operand. Operands in the range –256 to 255 can be represented using one prefix instruction.

The prefix instructions have important consequences.

- Firstly, they simplify language compilation, by providing a completely uniform way

of allowing any instruction to take an operand of any size up to the processor

word-length.

- Secondly, they allow operands to be represented in a form independent of the word-length of the processor.

#### 4.3 Indirect function

opr operate

One function (*opr*) causes its operand to be interpreted as the operation code of the instruction to be executed. This selects an operation to be performed on the values held in the evaluation stack. This allows up to 16 operations to be encoded in a single byte instruction. However, the prefix instructions can be used to extend the operand of *opr*, just like any other instruction.

To ensure that programs are represented as compactly as possible, the operations are encoded in such a way that the most frequent instructions are represented without using a prefix instruction.

#### 4.3.1 Notation

To aid clarity and brevity prefix sequences and the use of *opr* are not used in this guide. Each instruction is represented by a mnemonic, and for direct functions an item of data, which stands for the appropriate prefix sequence and function code. Also, where appropriate, an expression may be placed in a code sequence to represent the code needed to evaluate that expression.

### 4.4 Generating prefix sequences

Generating a prefix sequence for an operand is extremely tedious — especially when the operand is negative. Prefixing is intended to be performed by a compiler (or assembler) . Prefixing by hand is not advised!

Normally a value can be loaded into the operand register by a variety of different prefix sequences. It is clearly important to use the shortest possible sequence as this enhances both code compaction and execution speed — each prefix takes a cycle to execute. The best method of optimising object code so as to minimise the number of prefix instructions needed is shown below.

#### 4.4.1 Prefixing a constant

The algorithm to generate a constant operand e for a function op can be quite simply described by the following recursive function.

```

prefix (op, e) = IF  e < 16 \text{ AND } e \ge 0  op (e)  e \ge 16  prefix (pfix, e \gg 4); op (e \land \#F)  e < 0  prefix (nfix, (BITNOT e) \gg 4); op (e \land \#F)

```

where op (e) is the byte with function code op and data value e and  $\gg$  is a shift right.

#### 4.4.2 Evaluating minimal symbol offsets

Several instructions have an operand which is the offset between the current value of **lptr** and some other part of the code. Generating the optimal prefix sequence for the operand to one of these instructions is more complicated. This is because two, or more, instructions with offset operands can interlock so that the minimal prefix sequences for each instruction is dependent on the prefixing sequences used for the others.

For example consider the interlocking jumps below which can be prefixed in two distinct ways. The instructions

$$cj + 16; j - 257$$

can be coded as

but this can be optimised to be

This is because when the two offsets are decreased by 1 their prefixing sequences take 1 byte less so that the two interlocking jumps will still transfer control to the same instructions as before. This compaction of non-optimal prefix sequences is difficult to perform and a better method is to slowly build up the prefix sequences so that the optimal solution is achieved. The following algorithm will perform this.

- 1. Associate with each jump instruction or offset load an 'estimate' of the number of bytes required to code it and initially set them all to 0.

- Evaluate all jump and load offsets under the current assumptions of the size of prefix sequences to the jumps and offset loads

- For each jump or load offset set the number of bytes needed to the number in the shortest sequence that will build up the current offset.

- 4. If any change was made to the number of bytes required then go back to 2 otherwise the code has reached a stable state.

The stable state that is achieved will be the optimal state.

Steps 2 and 3 can be amalgamated so that the number of bytes required by each jump is updated as the offset is calculated. This does mean that if an estimate is increased then some previously calculated offsets may have been invalidated, but step 4 will force another loop to be performed when those offsets can be corrected.

By initially setting the estimated size of offsets to zero all jumps whose destination is the next instruction are optimised out.

Knowledge of the structure of code generated by the compiler will allow this process to be performed on individual blocks of code rather than on the whole program. For example it will often be possible to optimise the prefixing in the code for the sub-components of a programming language construct before the code for the construct is optimised. When optimising the construct it will be known that the sub-components are already optimal so they can be considered as an unshrinkable block of code.

This algorithm may not be efficient for long sections of code whose underlying structure is not known. If no knowledge of the structure is available (e.g. in an assembler), all the code must be processed at once. In this case a code shrinking algorithm where in step one the initial number of bytes is set to twice the number of bytes per word is used. The prefix sequences will then shrink on each iteration of the loop. 1 or 2 iterations will produce fairly good code although this method will never produce optimal code as it will not correctly prefix the pathological example given above.

# 5 Sequential processes

A sequential process is executed using six registers, each one word long. The word length may be any number of bytes.

# 5.1 Registers

The registers are

lptr

pointer to next instruction to be executed

Wptr

contains pointer to current process workspace

Areg

evaluation stack

Breg

evaluation stack

Creg

evaluation stack

Oreg

operand register

The **Wptr** register is used as a base from which the local variables and channels of a process can be addressed. The byte selector of the **Wptr** should always be 0.

#### 5.1.1 Evaluation stack

Areg, Breg and Creg are organised as a three word stack. Instructions which load Areg first push Breg into Creg and Areg into Breg. Instructions which store Areg pop Breg into Areg and Creg into Breg, leaving Creg undefined. The effects of this are shown in figures 5.1 and 5.2.

| Before |   |                   | After |   |   |

|--------|---|-------------------|-------|---|---|

|        |   | push x onto stack |       |   |   |

| Areg   | = | a                 | Areg  |   |   |

| Breg   | = | b                 | Breg  | = | а |

| Creg   | = | С                 | Creg  | = | b |

Figure 5.1 Effect of pushing value onto register stack

| Before |   |   | After |   |                    |

|--------|---|---|-------|---|--------------------|

|        |   |   |       |   | a popped off stack |

| Areg   | = | а | Areg  | = | b                  |

| Breg   | - | b | Breg  | = | С                  |

| Creg   | = | С | Creg  | = | undefined          |

Figure 5.2 Effect of popping value from register stack

#### 5.2 Local variables and constants

```

ldc load constant

ldl load local variable

stl store local variable

ldlp load pointer to local variable

rev reverse

```

The most common operations performed by a program are loading and storing one of a small number of variables, and loading small literal values. The *ldc* instruction enables values between 0 and 15 to be loaded into the stack using a single byte instruction.

The *Idl, stl* and *Idlp* instruction all access locations in word addressed memory relative to the workspace pointer **Wptr**. The first 16 locations can be identified using a single byte instruction. A local variable held in workspace location *n* can be pushed onto the stack by

ldl n

and its address can be pushed by

ldlp n

The value of the variable can be set to a value popped from the stack by

stl n

rev swaps the contents of Areg and Breg.

# 5.3 Expression evaluation

Expression evaluation is performed using the evaluation stack. The evaluation of operators with two operands is performed by instructions which combine the values of **Areg** and **Breg**. The result is left in **Areg**, and **Creg** is popped into **Breg** leaving **Creg** undefined.

Evaluation of expressions sometimes requires the use of temporary variables in the process workspace, but the number of these can be minimised by careful choice of the evaluation order.

Let depth(e) be the number of stack locations needed for the evaluation of expression e, defined by

'infinite' should be taken as meaning greater than any finite depth. The code generation for a function call is described in a following section.

A constant expression C is compiled by

```

Idc C

```

or by loading from a constant table as just described. A local simple variable expression x is compiled by

```

ldi x

```

Compilation methods for non-local variables, array elements and function calls are given in later sections.

Let commutes(op) be true if op commutes and false otherwise. Let e1 and e2 be expressions. The evaluation of e1 op e2 is performed by

```

IF

depth(e2) > depth(e1)

IF

depth(e1) > 2

(e2; stl temp; e1; ldl temp; op)

commutes(op)

(e2; e1; op)

TRUE

(e2; e1; rev; op)

depth(e2) < 3

(e1; e2; op)

TRUE

(e2; stl temp; e1; ldl temp; op)</pre>

```

where (11; 12; ...; In) represents a sequence of instructions.

In the cases where a temporary variable temp is required in the evaluation of e1 op e2 to hold the value of e2 then that variable can be used as a temporary variable in the evaluation of e2. Also a temporary variable used in the evaluation of e2 and not used to hold the result of e2 during the evaluation of e1 op e2 can be used in the evaluation of e1.

If it is known that all 3 registers on the register stack are available — i.e. there is not another evaluated expression already there — and depth(e2) is 2 then the branch

```

e2; e1; rev; op

```

can be optimised by using the code

```

e1; e2; op

```

removing the execution of the rev instruction.

#### 5.3.1 Loading operands

All three registers of the evaluation stack are used to hold the operands of certain instructions, and the first three parameters of procedure calls. Evaluation of an operand or parameter may involve the use of more than one register. Care is needed when evaluating such operands to ensure that the first operand to be loaded is not pushed off the bottom of the register stack by the evaluation of later operands.

Three registers are available for loading the first operand, two registers for the second and one for the third. Consequently, the instructions are designed so that **Creg** holds the operand which — on average — is the

|   | Registers required |        |    | Temp |   | Load<br>seq | Instructions                       |  |  |

|---|--------------------|--------|----|------|---|-------------|------------------------------------|--|--|

| ( | 9                  | В      | Α  | b    | а |             |                                    |  |  |

| ≤ | 2                  | 1      | 1  |      |   | 1           | C; B; A                            |  |  |

|   |                    | 1      | 2  |      |   | 2           | C; A; B; rev                       |  |  |

|   |                    | 1      | >2 |      |   | 4           | A; C; rev; B; rev                  |  |  |

|   |                    | 2      | 1  |      |   | 1           | C; B; A                            |  |  |

|   |                    | 2      | 2  |      | * | 1           | A; stl a; C; B; ldl a              |  |  |

|   |                    | 2      | >2 |      | * | 1           | A; stl a; C; B; ldl a              |  |  |

|   |                    | >2     | 1  |      |   | 3           | B; C; rev; A                       |  |  |

|   |                    | >2     | 2  |      | * | 3           | A; stl a; B; C; rev; ldl a         |  |  |

|   |                    | >2     |    |      | * |             | A; stl a; B; C; rev; ldl a         |  |  |

| > | 2                  | 1      | 1  |      |   | 1           | C; B; A                            |  |  |

|   |                    | 1      | 2  |      |   | 2           | C; A; B; rev                       |  |  |

|   |                    | 1      | >2 |      | * | 1           | A; stl a; C; B; ldl a              |  |  |

|   |                    | 2      | 1  |      |   | 1           | C; B; A                            |  |  |

|   |                    | 2<br>2 | 2  |      | * | 1           | A; stl a; C; B; ldl a              |  |  |

|   |                    | 2      | >2 |      | * | 1           | A; stl a; C; B; ldl a              |  |  |

|   |                    | >2     | 1  | *    |   | 1           | B; stl b; C; ldl b; A              |  |  |

|   |                    | >2     | 2  | *    |   | 2           | B; stl b; C; A; ldl b; rev         |  |  |

|   |                    | >2     | >2 | *    | * | 1           | A; stl a; B; stl b; C;ldl b; ldl a |  |  |

Table 5.1 Register loading sequences

most complex, and Areg the operand which is the least complex.

In some cases, it is necessary to evaluate the **Areg** and **Breg** operands in advance, and to store the results in temporary variables. This can sometimes be avoided using the reverse instruction. The following sequences may be used to load the operands *A*, *B* and *C* into **Areg**, **Breg** and **Creg**.

- 1. C: B: A

- 2. C: A: B: rev

- 3. B; C; rev; A

- 4. A; C; rev; B; rev

The choice of loading sequence, and of which operands should be evaluated in advance is determined by the number of registers required to evaluate each of the operands. In particular, if *C* requires more than two registers it must be loaded before *A* and *B*. If *A* or *B* requires more than two registers it must be evaluated before *C* and may need to be stored in a temporary variable if *C* requires more than two registers.

Table 5.1 gives the instruction sequences needed for loading three operands into the operand stack.

#### 5.3.2 Single length signed arithmetic

Single length arithmetic with error (overflow) checking is provided by the operations

add addition

sub subtraction

mul multiplication

div division

rem remainder

Of these, add and mul are commutative.

The instruction sequence

Idl X; Idl Y; op

where op is one of the arithmetic operations, evaluates the expression

X op Y

i.e. it takes the value in Breg as the lefthand operand and the value in Areg as the righthand operand.

#### 5.3.3 Adding a constant

The instruction

adc add constant

allows a constant value c to be added to Areg by adc c. Overflow is checked.

# 5.3.4 Single length modulo arithmetic

Single length arithmetic (with carry and overflow ignored) is provided by

sum addition diff subtraction prod multiplication

Of these, *sum* and *prod* are commutative. However, the time taken for *prod* is proportional to the logarithm of its second (**Areg**) operand, so if c is a small positive constant, performance can be improved by implementing both  $(c \times e)$  and  $(e \times c)$  as

e; c; prod

This is particularly important when multiplication forms part of a subscript expression, as described below.

prod has been modified on the IMS T800 to give a similar fast multiplication if Areg is a small negative value.

#### 5.3.5 Unary minus

The expression (-e) can be evaluated with overflow checked by

e; not; adc 1

or

Idc 0; e; sub

The first, using *not*, has the advantage of not needing an extra register.

The expression can be evaluated without overflow checking by

Idc 0: e: diff

#### 5.3.6 Fractional arithmetic

Many applications, such as scientific function evaluation, currently use fixed point arithmetic. To enable this to be performed efficiently on transputers the fractional multiply instruction has been added to 32 bit transputers — i.e. the IMS T414, IMS T800 and their derivatives.

fmul fractional multiply

*fmul* is a commutative arithmetic operator that interprets **Areg** and **Breg** as fixed point numbers lying in the range  $-1 \le x < 1$ . The value associated with the register is  $2^{-31}$  times its signed integer value. *fmul* returns the rounded fixed point product of these values in **Areg** and pops **Creg** up into **Breg**. The rounding is performed in *Round-to-Nearest* mode as in ANSI/IEEE 754-1985 arithmetic.

Attempting  $(-1) \times_{frac} (-1)$  sets the error flag as +1 cannot be represented in this format — this is the only case in which *fmul* can overflow.

#### 5.3.7 Logic and shifts

Bitwise operations and shifts are provided by

and bitwise and

or bitwise or

xor bitwise exclusive or

not bitwise not shl shift left

shr shift right

Of these, and, or and xor are commutative. The not operation has only one operand.

The shift operations shift the operand in **Breg** by the number of bits specified in **Areg**. Vacated bit positions are filled with zero bits. The result is the initial value of **Breg** if **Areg** is zero. The instruction takes time proportional to the value of **Areg** to execute taking one cycle for every bit shifted plus a small initial overhead. The worst case can cause a transputer to 'lock' for 3 to 4 minutes. **Areg** can be checked to signal an error on out of range shifts using the *csub0* operation which is described later. The comparison instructions described later can also be used to 'short circuit' these out of range shifts so that a 0 is returned when the shift length is greater than the number of bits in a word without the actual shift instruction being executed.

## 5.4 Arrays and subscripts

The addressing instructions provide access to items in data structures using short sequences of single byte instructions. They also allow the representation of data structure access to be independent of the wordlength of the processor.

bcnt byte count wcnt word count

The *bcnt* instruction multiplies **Areg** by the number of bytes in a word. It is particularly used for producing the length in bytes of a multiword data item. The *wcnt* instruction enables an address to be decomposed into its component word part and byte selector. *wcnt* takes an address in **Areg** and returns the word offset from 0 in **Areg** and the byte selector in **Breg**.

# 5.4.1 Forming addresses

Idpi load pointer to instructionmint load most negative integer

bsub byte subscriptwsub word subscript

The address of a data structure held in the local workspace is loaded using the *Idlp* instruction that has already been introduced.

The address of a location in the program can be obtained by the ldpi operation so that relocatable code can be generated. A location which is x bytes from the byte location of the next instruction can be pushed onto the stack by

ldc x; ldpi

The address of a label L: can be loaded by

The most negative address can be pushed onto the stack by *mint*. This is particularly useful for forming the address of a communication link.

Both the *bsub* and *wsub* instructions interpret **Areg** as the address of the beginning of a data structure. The result of *bsub* is the address of the byte which is **Breg** bytes from the beginning of the structure. Similarly, the result of *wsub* is the address of the byte which is **Breg** words from the beginning of the structure.

#### 5.4.2 Structures

M:

The 'local' operations *IdI*, *stI* and *IdIp* access word addresses relative to **Wptr**. This is useful for accessing local scalar variables. For accessing elements of structures a level of indirection is required.

#### Non local variable access

An element in a structure is accessed by calculating the offset of the element from the base address of that structure.

IdnI

load non local variable

stnI

store non local variable

IdnIp

load pointer to non local variable

These 'non local' operations operate in a similar way to their 'local' counterparts except that they access a word address relative to **Areg** rather than **Wptr**. **Areg** must contain a valid word address, so its byte selector must be 0 for the instruction to be defined.

The base address in **Areg** is popped off the stack. In the case of *IdnI* and *IdnIp* the result is pushed into **Areg** replacing the original base address, while for *stnI* **Breg** is also popped out of the stack and is stored.

Access to a component of a structure can be split into two sections. Firstly the address of the component must be constructed, and then the transfer of data to or from that component must be performed.

# **Evaluating a subscript**

Array subscripts can be evaluated efficiently using the prod instruction. If array A has been declared by

$$[S_1] \dots [S_n]$$

INT A:

and an access is required to

$$A[e_1] \dots [e_n]$$

then the code to evaluate the subscript is

```

Idc S_2; e_1; prod; e_2; add; Idc S_3; prod; ...; e_n; add

```

As *prod* takes time proportional to the logarithm of the value in **Areg** the code is arranged so that the smaller operand to the *prod* is in **Areg**. This will be the actual subscript for the first *prod* but will be the subscript range for all the other times. All the array multiplications will be done in time proportional to the logarithm of the subscript size — which usually will be fairly small. There is no need for the multiplication to check for overflow as this should be checkable during compilation. Mechanisms for range checking the actual subscripts are given later.

#### Accessing a word addressed structure

Let *Wa* be a structure which starts at a word address and in which all component types are measured in words. Let *e* be a subscript expression. The address of component *e* of *Wa* is

e; Wa; wsub

or

Wa; Idnlp e

if e is a constant expression.

#### Accessing a byte addressed structure

Similarly, let Ba be a structure in which each component type is measured in bytes, and e a subscript expression. Then the address of component e of Ba is

e: Ba: bsub

# 5.4.3 Transferring structure elements

Once the address of the structure element has been evaluated its length in bytes is required to enable it to be transferred using one of the transfer instructions.

move move block in input block out output block

Let Xb be a variable or expression with length in bytes given by the value of the expression b. Then

$$length(Xb) = b$$

Let Xw be a variable or expression of length in words given by the value of the expression w. Then

$$length(Xw) = w$$

;  $bcnt$

If the value of w, and the target wordlength are both known to the compiler, then

```

length(Xw) = ldc (w \times Bytesinword)

```

Assignment of structures is achieved with the block move instruction *move*. It moves **Areg** bytes of data starting at address **Creg** to address **Breg**.

```

v1 := v2 = address(v2); address(v1); length(v1); move

```

where address(v) is translated as described above. The two structures must not overlap — if they do, the effect of the move instruction is not defined. In particular the move instruction can not be used to initialise a region of memory by moving from one location to an adjacent location. move is undefined if the value in **Areg** is negative.

Input is achieved by means of the input message instruction in. This transfers a communication of **Areg** bytes from channel **Breg** to address **Creg**. For example

```

c ? v = address(v); address(c); length(v); in

```

Output of a variable is performed by means of the output message instruction *out*. This transfers a communication of **Areg** bytes from address **Creg** to channel **Breg**. For example

```

c ! v = address(v); address(c); length(v); out

```

Both the input and output ends of a communication should have the same value in Areg when executing the in and out otherwise the effect of the communication is undefined.

On current transputers if different lengths are used then on an internal communication the amount of data transferred will be determined by the second process to be ready — so that if this is *out* with the longer length the message can corrupt the other process' data by overwriting. If different lengths are used on an

external communication then the process with the shorter message length will behave as if it has communicated successfully while the other process will still be waiting to finish its communication. If the length of a communication is variable then some protocol by which the length is communicated before the actual message is needed.

The effects of the communication instructions are undefined if the message length is negative or 0. Methods for range and sign checking are given later.

# Single word and byte transfer

The common cases of single word and byte transfer can be optimised.

#### Byte transfer

```

lb load bytesb store byteoutbyte output a single byte

```

*Ib* and *sb* load and store to the byte at the address in **Areg**. *Ib* replaces the address in **Areg** with the byte value stored at that address. *sb* stores the byte value in **Breg** at the address in **Areg** and pops **Creg** up into **Areg**. *outbyte* communicates the single byte in **Areg** down channel **Breg**. *outbyte* uses location (**Wptr**+0) as a temporary variable.

So if a and b are both single byte elements and e is a byte valued expression then compiled code for the transfers are

```

b := a = address(a); lb; address(b); sb

b := e = e; address(b); sb

c ? b = address(b); address(c); ldc 1; in

c ! e = address(c); e; outbyte

```

#### Word transfer

```

outword output a single word

```

outword communicates the single word in Areg down channel Breg. outword uses location (Wptr+0) as a temporary variable.

So if x and y are both single word elements and e is a word valued expression then compiled code for the transfers are

```

x := y = | dd | y; st | x

x := e = e; st | x

c ? x = address(x); address(c); | dc | 1; bcnt; in

c ! e = address(c); e; outword

```

When the target wordlength is known, channel input can be optimised as

```

address(x); address(c); ldc bytesperword; in

```

# 5.5 Assignment

Previous sections have detailed how single assignments to variables, array elements and arrays can be compiled. The compilation of multiple assignments is more complex.

## 5.5.1 Multiple assignment

In occam the multiple assignment

$$V_1, \ldots, V_n := E_1, \ldots, E_n$$

is defined as being equivalent to

```

T_1 \ temp_1:

\vdots

T_n \ temp_n:

SEQ

PAR

temp_1 := E_1

\vdots

temp_n := E_n

PAR

V_1 := temp_1

\vdots

V_n := temp_n

```

where the parallel separation rules of occam apply so that multiple assignments are restricted to those whose 'expanded' version is a valid occam program.  $T_1 \dots T_n$  are type definitions of the appropriate types.

Because the final assignments are performed as if in a **PAR** construct they are guaranteed not to interfere — i.e. one assignment cannot affect the destination of another — so that they can be compiled as a sequence of assignments. Hence the multiple assignment can be compiled as

```

assign(temp_1, E_1); \dots; assign(temp_n, E_n); \\ assign(V_1, temp_1); \dots; assign(V_n, temp_n)

```

where

represents the compiled code for

$$V := E$$

This can be optimised by re-ordering the two assignment sequences to enable registers to be used instead of some of the temporary variables.

# 5.6 Comparisons and conditional behaviour

Comparisons and conditional behaviour are provided by

```

eqc equal to constant

gt greater

```

together with

```

j jump

ci conditional jump

```

#### 5.6.1 Comparison

The eqc instruction loads **Areg** with a truth value — true if **Areg** is initially equal to the instruction operand, false otherwise. Similarly, the gt instruction loads the A register with true if **Breg** > **Areg**, false otherwise. true and false are represented by 1 and 0 respectively, and therefore can be loaded with single byte load constant instructions.

It is also possible to represent true by a value other than 1. In particular, using

```

eac X: not: adc 1

```

and

gt; not; adc 1

in place of eqc X and gt will permit -1 to be used to represent true.

#### 5.6.2 Jump and conditional jump

The jump instruction, j, adds its operand to the address of the instruction immediately after it and puts the result into **lptr**, thus transferring execution to another part of the program. The conditional jump instruction, cj, performs a jump if the value in **Areg** is 0 but otherwise pops the value in **Areg** off the register stack and continues with the next instruction. Consequently the cj instruction serves as 'jump if false'.

The *j* instruction will deschedule the process if the current timeslice has been exceeded, ensuring that there is an opportunity to deschedule once each time round a loop. Since a process can be descheduled by timeslicing on an unconditional jump, *j*, it is important that no information is held in the register stack at this point since if the process is descheduled the information will be corrupted by the next process that is scheduled.

The ci instruction never deschedules the process. The sequence

```

Idc 0; cj L

```

can be used in place of

j L

if it is important that descheduling does not occur. This will cause the value 0 to have been pushed onto the register stack when execution reaches *L*. This 0 value can be removed, if necessary, by making the first instruction after *L* a *diff* which will restore **Areg** and **Breg** to the values they held before the jump — however any value in **Creg** will have been lost.

#### 5.6.3 Fast evaluation of boolean expressions

The cj instruction can be used to provide 'short circuit' evaluation of boolean expressions. The following table shows the correspondence between occam expressions and instructions. X and Y are expressions, and K a constant expression.

TRUE =

$$|dc\ 1|$$

FALSE =  $|dc\ 0|$

NOT  $X = \neg(X)$

$X \text{ OR } Y = \neg(\neg(X); cj\ L; \neg(Y); L:)$

$X \text{ AND } Y = X; cj\ L; Y; L:$

$X = Y = X; Y; diff; eqc\ 0$

$X <> Y = \neg(X; Y; diff; eqc\ 0)$

$X = K = X; eqc\ K$

$X <> K = \neg(X; eqc\ K)$

$X > Y = X; Y; gt$

$X < Y = Y; X; gt$

$X <= Y = \neg(Y; X; gt)$

$X <= Y = \neg(X; Y; gt)$

where

$$\neg(\neg(X)) = X$$

$$\neg(X) = (X; eqc 0)$$

#### 5.6.4 Conditional transfer of control

The conditional expressions used in each conditional branch of an IF construct are translated as follows

$$E = E; cj L;$$

$P P; j END;$

$L:$

where the label END: is at the end of the code for the IF construct.

The compilation of a WHILE loop is

Note that this loop includes an unconditional jump. The presence of this ensures that rescheduling can take place should the loop continue for longer than a single time-slice.

#### 5.6.5 Optimisation of conditional transfer

The following laws should be applied to the compilation of conditional expressions before code is generated to ensure that the jump is taken as early as possible.

```

\neg(X \text{ AND } Y) = \neg(X) \text{ OR } \neg(Y) \\

\neg(X \text{ OR } Y) = \neg(X) \text{ AND } \neg(Y) \\

(X \text{ OR } Y); cj L = \neg(X); cj M; Y; cj L; M: \\

(X \text{ AND } Y); cj L = X; cj L; Y; cj L \\

X = Y; cj L = X; Y; diff; cj L \\

X = 0; cj L = X; cj L

```

# 5.6.6 Compiling CASE statements

The CASE statement is a special form of conditional transfer where the transfer is determined by comparing an expression to a number of constants.

When compiling the process

```

CASE X

```

the expression x is evaluated and stored in a local variable by

```

x; stl selector

```

Then each branch of the CASE statement

$$c_1, \ldots, c_n$$

$P$

can be compiled by

```

Idl selector; Idc c<sub>1</sub>; diff; cj L;

Idl selector; Idc c<sub>2</sub>; diff; cj L;

...

Idl selector; eqc c<sub>n</sub>; cj M;

L: P; j END;

M:

```

where the label END: is placed at the end of the CASE statement.

#### Optimised compilation of CASE

The compilation method given above will produce inefficient code for large CASE statements. To produce more efficient code the following rules can be used.

First build up a set of pairs of selector values and processes, consisting of every selector value in the **CASE** statement along with its associated process — the process part of each pair can be represented by the offset to the start of the compiled code for that process. Then the following rules can be used.

- 1. If there are 3 entries or less then use the same method as described above.

- If there are 12 entries or less then use a binary search to limit the number of comparisons required.

- 3. For more than 12 entries attempt to use a jump table. The offset of the start of each selected process is placed in the table against each selector value. Entries that do not match a selector in the CASE statement must contain the offset of an error handler process. This jump table should be the largest table such that about <sup>1</sup>/<sub>3</sub> of the entries are filled. This compilation strategy is then recursively called to handle the two ends. The *gcall* and *ldpi* instructions, described later, can be used to jump to the selected piece of code.

The choice of 3 or less processes, 12 or less processes and  $\frac{1}{3}$  filled table are the values used in current INMOS occam compilers.

Consider compiling the CASE expression

where, for brevity, it is assumed that all the case selectors are already in increasing order.

#### Three entries or less

This case is compiled as

$$X = c_1$$

$$P_1$$

$$\vdots$$

$$X = c_n$$

$$P_n$$

#### Four to twelve entries

This case is compiled as

```

IF

X <= c_{\frac{n}{2}}

IF

X <= c_{\frac{n}{4}}

... etc.

X > c_{\frac{n}{4}}

... etc.

X > c_{\frac{n}{2}}

... etc.

```

#### Using a jump table

Assume that  $c_{\rm i}$  ...  $c_{\rm m}$  form a  $\frac{1}{3}$  filled jump table. Then the case is compiled as

```

IF

X < c_i

CASE X

C_1

P_1

\vdots

C_{i-1}

P_{i-1}

X > c_m

\ldots similar

TRUE

\ldots jump table code

```

where jump table code is

```

X; ldc\ c_i; diff; ldc\ jump\_size; prod; ldc\ (jump\_table\_M); ldpi M: bsub; gcall; jump\_table: j\ case\_0; j\ case\_1; ...; j\ case\_k ERROR: ... error\ code Li: ... code\ for\ P_i \vdots Lm: ... code\ for\ P_m

```

The code at *ERROR* should be the same code as used at the end of a **IF** statement where all the conditionals have been false. The *wsub*, *Idpi* and *gcall* instructions are explained in later sections.

The code at jump\_table consists of a sequence of jump instructions which transfer control to the relevant branch  $Li \ldots Lm$  or to ERROR. The destination,  $case\_x$ , of each of these jumps is Lj if  $c_j$  is equal to  $(c_i + x)$  and is ERROR otherwise.

All the jumps in the *jump\_table* code are prefixed to be the same length (*jump\_size* bytes) to enable them to be accessed as a byte array.

# 5.7 Long arithmetic and shifts

# 5.7.1 Multiple length addition and subtraction

Signed addition and subtraction can be performed on values longer than a word using the instructions

ladd long add lsub long subtract lsum long sum ldiff long difference

The *ladd* and *lsub* instructions are used for the final step of a signed multiple length addition or subtraction. The other steps can be performed using *lsum* and *ldiff*. For all four instructions, there are two unsigned single word operands held in **Areg** and **Breg**, and a carry (or borrow) operand held in the least significant bit of **Creg** (**Creg**<sub>lsb</sub>).

The ladd instruction sets Areg to (Breg + Areg) + Cregist. Arithmetic overflow is checked.

The Isub instruction sets Areg to (Breg - Areg) - Creg<sub>isb</sub>. Arithmetic overflow is checked.

The *Isum* instruction forms (**Breg** + **Areg**) + **Creg**<sub>Isb</sub> leaving the least significant word of the result in **Areg** and the most significant (carry) bit in **Breg**.

Similarly, the *Idiff* instruction forms (Breg - Areg) -  $Creg_{lsb}$  leaving the least significant word of the result in Areg and the borrow bit in Breg.

Addition of two double length signed values with overflow checking can therefore be translated as follows

```

Idc 0;

Idl X_{lo}; Idl Y_{lo}; Isum; stl Z_{lo};

Idl X_{hi}; Idl Y_{hi}; Iadd; stl Z_{hi}

```

Subtraction of two double length values without overflow checking is translated as

```

Idc 0;

Idl X_{lo}; Idl Y_{lo}; Idiff; stl Z_{lo};

Idl X_{hi}; Idl Y_{hi}, Idiff; stl Z_{hi}

```

with the final borrow left in Areg.

#### 5.7.2 Multiple length multiplication and division

The long multiplication and division instructions are

```

Imul long multiply Idiv long divide

```

The *Imul* instruction multiplies two single word unsigned operands in **Areg** and **Breg**, and adds the single word 'carry' operand in **Creg** to form a double length unsigned result. The most significant (carry) word of the result is left in **Breg**, the least significant in **Areg**. No overflow is possible so the error flag is not affected by this instruction. Multiplication of a single length unsigned value X by a double length unsigned value Y can be performed by

```

Idc 0;

Idl X; Idl Y_{lo}; Imul; stl Z_{lo};

Idl X; Idl Y_{hi}; Imul; stl Z_{hi}

```

which leaves the 'carry' in Areg.

Double length unsigned multiplication can be performed by

```

\begin{array}{l} \textit{Idc 0;} \\ \textit{Idl $X_{lo}$; Idl $Y_{lo}$; Imul; stl $Z_0$} \\ \textit{Idl $X_{lo}$; Idl $Y_{hi}$; Imul; rev; stl $Z_2$} \\ \textit{Idl $X_{hi}$; Idl $Y_{lo}$; Imul; stl $Z_1$;} \\ \textit{Idl $X_{hi}$; Idl $Y_{hi}$; Imul; rev; stl $Z_3$;} \\ \textit{Idc 0; rev; Idl $Z_2$; Isum; stl $Z_2$;} \\ \textit{Idl $Z_3$; sum; stl $Z_3$} \end{array}

```

This multiplies the two double length values X and Y to produce the quadruple length result Z. Signed

multiplication can be derived from this by performing the relevant overflow checking tests on this quadruple length result before storing the bottom two words.

The *Idiv* instruction divides the double length unsigned value held in **Breg** and **Creg** (most significant word in **Creg**) by the single length unsigned value in **Areg**. The result is left in **Areg** with the remainder in **Breg**. Overflow occurs if the result cannot be represented as an unsigned single word value and causes the error flag to be set. Division of a double length value X by a single length value Y to produce a double length result Z can be performed by

```

Idc 0;

Idl X<sub>hi</sub>; Idl Y; Idiv; stl Z<sub>hi</sub>;

Idl X<sub>lo</sub>; Idl Y; Idiv; stl Z<sub>lo</sub>

```

which leaves the remainder in Area.

#### 5.7.3 Multiple length shifts

The long shift instructions are

```

IshI long shift left Ishr long shift right

```

The *IshI* and *Ishr* instructions both shift the double length value held in **Breg** and **Creg** (most significant word in **Creg**). Vacated bit positions are filled with zero bits. The number of bit positions shifted is the value of **Areg**, the result is the unshifted value if **Areg** is zero, and is undefined if **Areg** is less than zero or greater than the number of bits in a double length value. The value of **Areg** can be checked in advance by using the *csub0* instruction. The result is left in **Areg** and **Breg** (most significant word in **Breg**).

A double length value X can be shifted Y places left by

```

Idl Xhi; Idl Xlo; Idl Y; Ishl; stl Xlo; stl Xhi

```

Like the single length shifts, the shift length should be checked if there is a possibility that it is greater than twice the wordlength, to prevent a transputer being 'locked' for a significant time by an 'out of range' shift.

A double length value X can be shifted Y places right with the shift length checked by the following code. This will set the error flag if the shift length is not in the range  $0 \dots 2 \times wordlength$ .

```

Idl\ Y; Idc\ (2 \times wordlength + 1); csub0; Idl\ X_{hi}; Idl\ X_{lo}; Idl\ Y; Ishl; stl\ X_{lo}; stl\ X_{hi}

```

#### Single length arithmetic shifts

A single length value X can be arithmetically shifted Y places right by

```

Idl X; xdble; Idl Y; Ishr; stl X

```

and by Y places left by

```

Idl X; xdble; Idl Y; Ishl; csnql; stl X

```

where xdble and csanl are explained in a later section.

#### Single length rotation

A single length value X can be rotated Y places right by

```

Idl X; Idc 0; Idl Y; Ishr; or; stl X

```

and by Y places left by

```

Idc 0; Idl X; Idl Y; Ishl; or; stl X

```

If the rotate length is not guaranteed to lie in the range  $0 \le Y < wordlength$  then the length should be masked with (wordlength - 1). This is because the *lshl* or *lshr* will lose the bits in the word being rotated. wordlength can be evaluated by

```

Idc 8: bcnt

```

bent multiplies the value in Areg by the number of bytes per word.

The long shifts can also be used to perform extraction and insertion of bit fields, even where these cross word boundaries in memory.

#### 5.7.4 Normalising

norm normalise

The *norm* instruction normalises the unsigned double length value in **Areg** and **Breg** (most significant word in **Breg**). The double length value held in **Areg** and **Breg** is shifted left until the most significant bit of the value is one. The shifted double length value remains in **Areg** and **Breg**. The number of bits shifted is left in **Creg**. If the double length value is initially zero, **Creg** is set to twice the number of bits in a word.

#### 5.8 Integer length conversion

Conversion between signed values of different lengths can be performed using

xwordcwordcheck wordxdblecsnglcheck single

#### 5.8.1 Conversion between partword values and word values

The *xword* instruction sign extends a partword value to a single word value. The *cword* instruction checks that a single word value can be represented by a partword value. A partword value is assumed to be of any length between one bit and the number of bits in a word. It occupies the least significant bits in a word. For both instructions, the length of the partword is specified by the bit pattern of the most negative integer representable in the partword.

The two operands of the xword instruction are a partword in **Breg** and a length specified by **Areg**. A signed

byte value can therefore be extended to a word value by

```

Idc #80; xword

```

Similarly, the two operands of the *cword* instruction are a single word value in **Breg** and a length specified in **Areg**. The result, left in **Areg**, is the (unchanged) value of **Breg** and the error flag is set if the value cannot be represented in the partword. A signed byte value can be checked by

```

Idc #80: cword

```

Two signed three bit values X and Y can be added and checked for overflow by

```

X; ldc #4; xword;

Y; ldc #4; xword;

add; ldc #4; cword

```

## 5.8.2 Conversion between single word values and multiple word values

The *xdble* instruction sign extends the single length signed value in **Areg** into a double length signed value in **Areg** and **Breg** (most significant word in **Breg**). Conversely, *csngl* reduces the double length signed value in **Areg** and **Breg** into a single length signed value in **Areg**. The error flag is set if the double length value falls outside the range of values representable in a single word.

# 5.9 Replication

Replicators are implemented by using the loop end instruction.

```

lend loop end

```

A loop is controlled by two contiguous words in memory. The first contains the value of the control variable and the second contains the unsigned number of iterations left to perform. The *lend* instruction interprets **Breg** as a pointer to such a control block and **Areg** as the number of bytes from the start of the next instruction to the start of the loop. The start of the loop normally will be before the *lend* instruction in memory so, to avoid the need for an *nfix* instruction, this offset is measured in the opposite direction from other offsets.

lend will decrement the iteration count and, if the number of iterations remaining is greater than zero, increment the control variable and subtract **Areg** from **lptr**. If the number of iterations left after the decrement is less than or equal to zero then execution passes to the next instruction. Note that, like the jump instruction, the loop end instruction will cause rescheduling if the looping process has exceeded its timeslice, again ensuring that there is an opportunity to timeslice each time round a loop. Because of this **Creg** should not be used to hold information when *lend* is executed as, if the process is descheduled, the information will be lost.

As an example take the replicated SEQ construct. The compilation of the occam replicated SEQ is

```

SEQ i = start FOR count start; stl i; count; stl i+1; ldl i+1; cj END;

L: P; ldlp i; ldc (END-L); lend; END:

```

Where it is clear that count is not zero the following may be used

```

SEQ i = start FOR count start; stl i; count; stl i+1;

P L: P; Idlp i; Idc (END-L); Iend;

END:

```

The same basic instruction sequence is used to construct the loop in an occam replicated IF, ALT or PAR, and to initialise arrays of channels.

The count of iterations to perform should be positive. When the number of iterations is the result of an expression then it may be necessary to add some range checking to cause an error or ignore the loop if this evaluates to a negative value. If the count is negative then the loop would execute once before the *lend* instruction caused the loop to end. A negative count value should probably be treated as an error, though this depends on the definition of loops in the language being compiled.

## 5.10 Procedures

The instructions

call call

gcall general call ajw adjust workspace

gajw general adjust workspace

ret return

are used to implement procedures.

The *ajw* adjusts the value of the workspace pointer by the number of words in its operand value. Workspace is claimed by using a negative value and released by using a positive value.

The *call* instruction adjusts the workspace pointer, allocating four new locations into which it stores the three evaluation stack registers and the instruction pointer — this return address is left in **Areg** by the instruction. The operand to the call is added to **lptr** to produce the address of the procedure being called.

The *ret* instruction restores the **lptr** and adjusts the workspace pointer to deallocate the four locations. A procedure which requires more space will normally include adjust instructions to allocate and deallocate space. When the *ret* instruction is executed any workspace claimed by the procedure should have been released so that the **Wptr** has returned to the value it held at the start of the procedure. The *ret* instruction does not affect the evaluation stack, and it is therefore possible to return up to three values to the calling procedure.

The state of the workspace after the call instruction is as shown below

|        |              | Saved values |

|--------|--------------|--------------|

| Wptr+4 | (= old Wptr) |              |

| Wptr+3 |              | Creg         |

| Wptr+2 |              | Breg         |

| Wptr+1 |              | Areg         |

| Wptr+0 |              | lptr         |

## 5.10.1 Use of (Wptr+0)

The location (Wptr+0) is used as an extra 'register' by certain instructions. These are

outword, outbyte, postnormsn, and the instructions to implement ALT

Any procedure that uses one of these instructions must allocate an extra workspace slot for this use of **Wptr**+0 so that the return address is not overwritten. Workspace allocation is achieved by the *ajw* instruction.

## 5.10.2 Loading parameters

It is convenient to load the first three parameters of the procedure into the evaluation stack registers, and to arrange the workspace of the calling procedure so that the additional parameters can be stored in locations 0, 1, ... of the workspace before the procedure is called. In this way, the called procedure will be entered with its parameters stored in consecutive locations starting at workspace location 1. To enable the procedure to access non local variables the parameters of a procedure should include a link to the environment in which the procedure was declared.

#### 5.10.3 The static chain

The scope rules of block structured languages can be implemented using a static chain. This involves passing a single pointer as a parameter whenever a procedure is called. The 'non local' load, store and pointer operations described in a previous section can then be used to access variables declared in an enclosing block.

#### Variable access via the static chain

Access via the static chain is provided by the ldnl, stnl and ldnlp instructions. Let n be the lexical level of the current procedure, and  $S_i$  the offset of the lexical link at level i. Then access to a location x at level n-1 is provided by

```

Idl\ S_n; Idnl\ x to load a variable Idl\ S_n; Idnlp\ x to load a pointer to a variable Idl\ S_n; stnl\ x to store a variable

```

Similarly, access to a location y at level n-2 is

```

Idl S_n; Idnl S_{n-1}; Idnl y ... etc.

```

#### Forming a static link

When a procedure P is called, the static link for the call of P must be computed. Let n be the lexical level of the current procedure, and m the lexical level of P. If m = n+1 the new link is computed by  $(Idlp \ x)$  with x chosen so that P can access all of its global variables, channels etc. Otherwise the new link is computed as

the value of the link location at level m. With  $S_i$  as above, this can be obtained by

```

\begin{split} IF & m = n+1 \\ & ldlp \ x \\ m = n \\ & ldl \ S_n \\ m = n-1 \\ & ldl \ S_n; \ ldnl \ S_{n-1} \\ m = n-2 \\ & ldl \ S_n; \ ldnl \ S_{n-1}; \ ldnl \ S_{n-2} \\ & \cdots \\ & etc. \end{split}

```

#### Passing the static link as a parameter